Clock Synthesizer IP

Welcome to the ultimate Clock Synthesizer IP hub! Explore our vast directory of Clock Synthesizer IP

All offers in

Clock Synthesizer IP

Filter

Compare

69

Clock Synthesizer IP

from

16

vendors

(1

-

10)

-

Clock Buffer - X-FAB XT018-0.18µm BCD-on-SOI CMOS

- Max Load: 25pF total (including padcell and bondwire parasitics)

- Signal Integrity: Maintains tight rise/fall timing (1.4-3.1ns) across a wide load range (1pF to 26pF)

- Low Propagation Delay: 6ns typical delay at max load, ensuring fast response for real-time systems

- Efficient Power Use: 6.5mA average current at 40MHz with 25pF load, balancing performance and energy efficiency

-

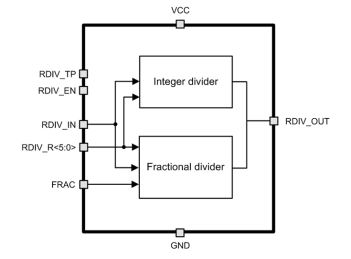

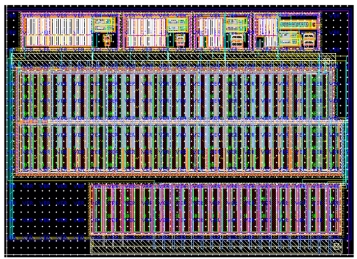

Frequency Divider

- Division ratio: any integer from 1 to 8/64/512/4096

- Maximum input frequency 2GHz – 10+GHz (A)

- Clock input and output signals are differential CMOS

- Control signals are single ended CMOS

-

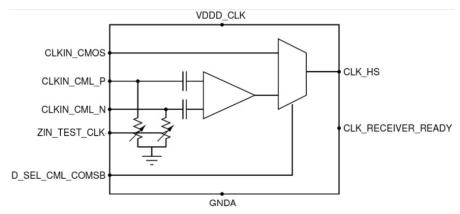

High-speed clock receiver operating up to 2.5 GHz with low output jitter

- The ODT-CRX-2P5G-16FFCT is a high-speed clock receiver circuit capable of operating up to 2.5 GHz with low output jitter.

- The CRX uses a high-speed signal path that can provide low jitter for input ranges of up to 2.5 GHz input. It also features small area and low power consumption. It includes the decoupling capacitors and ESD protection diodes on the CLKIN pins.

-

ULP Clock Generator - GLOBALFOUNDRIES 22FDX

- The All Digital Frequency Locked Loop (ADFLL) architecture is reduced to the minimum amount of hardware necessary to generate a 10 MHz clock

- High energy efficiency: Only 5 μW are consumed during operation

- A reference clock divider allows reference clock frequencies from 32 kHz to 1 MHz

-

ULP 10MHz Clock-Generator - GLOBALFOUNDRIES 22FDX

- The All Digital Frequency Locked Loop (ADFLL) architecture is reduced to the minimum amount of hardware necessary to generate a 10 MHz clock

- High energy efficiency: Only 5 μW are consumed during operation

- A reference clock divider allows reference clock frequencies from 32 kHz to 1 MHz

-

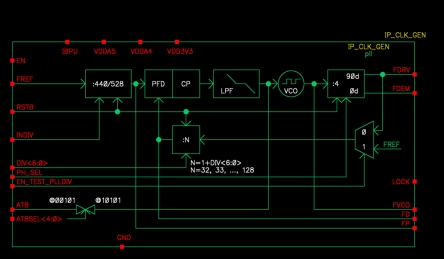

Integer-N-PLL-based HF Frequency Synthesizer and Clock Generator with integrated Loop Filter and VCO

- This integer-N PLL synthesizes 3.3V-square-wave FVCO frequencies within the HF range from 2.424MHz up to 9.697MHz, by steps of 18.9393kHz, and provides one fourth of fVCO on two other outputs, FDEM and FDRV, which feature quadrature phase difference or no phase shift depending on the control bit PH_SEL.

- The PLL-locked state within ±0.08% of fVCO is signaled by a logic high level on the LOCK output.

-

ULP Clock-Generator - GLOBALFOUNDRIES 22FDX

- ABB-enabled, All-Digital PLL clock generator for ultra-low power clocking in highly energy efficient Systems on Chip

- The Ultra-Low Voltage Clock Generator is targeted at Systems on Chip (SoCs) employing advanced power management techniques.

- The robust, fully digital architecture allows operation in a wide voltage and frequency range. Unique fast lock and instant frequency change features maximize the energy efficiency of the targeted systems.

-

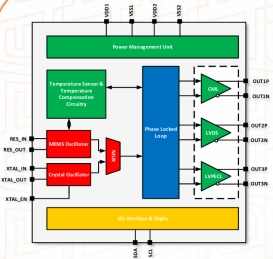

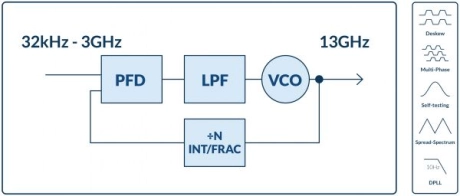

MEMS-based Clock Generator with On-chip Temperature Compensation

- The MVCLK02 is a high-precision and programmable clock generator circuit, with a wide output frequency range.

- The chip contains a versatile MEMS oscillator circuit that is designed to ensure high performance for a wide range of MEMS resonators and with different parameters.

-

General-purpose & Specialized Ring PLLs + RTL-based Solutions

- Wide functional range allows all frequencies in a system to be synthesized with one PLL macro

- Input & output frequency ranges greater than 1000:1

-

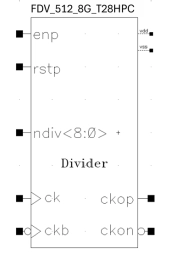

Programmable 6-bit CMOS frequency divider

- iHP SGB25V

- Range of dividing ratio 1…63

- Dividing ratio change with step 0.5

- Compact structure