SamurAI: a 1.7MOPS-36GOPS Adaptive Versatile IoT Node with 15,000x Peak-to- Idle Power Reduction, 207ns Wake-up Time and 1.3TOPS/W ML Efficiency

Ivan Miro-Panades1, Benoit Tain2, Jean-Frédéric Christmann1, David Coriat1, Romain Lemaire1, Clement Jany3, Baudouin Martineau3, Fabrice Chaix3, Anthony Quelen3, Emmanuel Pluchart1, Jean-Philippe Noel1, Reda Boumchedda3,4, Adam Makosiej3, Maxime Montoya3, Simone Bacles-Min1, David Briand2, Jean-Marc Philippe2, Alexandre Valentian1, Frédéric Heitzmann3, Edith Beigne3, Fabien Clermidy1

1 Univ. Grenoble Alpes, CEA, LIST, Grenoble, France;

2 Univ. Paris-Saclay, CEA, LIST, Gif sur Yvette, France;

3 Univ. Grenoble Alpes, CEA, LETI, Grenoble, France;

4 STMicroelectronics, Crolles, France

Abstract

IoT node application requirements are torn between sporadic data-logging and energy-hungry data processing (e.g. image classification). This paper presents a versatile IoT node covering this gap in processing and energy by leveraging two on-chip sub-systems: a low power, clock-less, event-driven Always-Responsive (AR) part and an energy-efficient On- Demand (OD) part. The AR contains a 1.7MOPS event-driven, asynchronous Wake-up Controller (WuC) with 207ns wake-up time optimized for short sporadic computing. OD combines a deep-sleep RISC-V CPU and 1.3TOPS/W Machine Learning (ML) and crypto accelerators for more complex tasks. The node can perform up to 36GOPS while achieving 15,000x reduction from peak-to-idle power consumption. The interest of this versatile architecture is demonstrated with 105μW daily average power on an applicative classification scenario.

Introduction

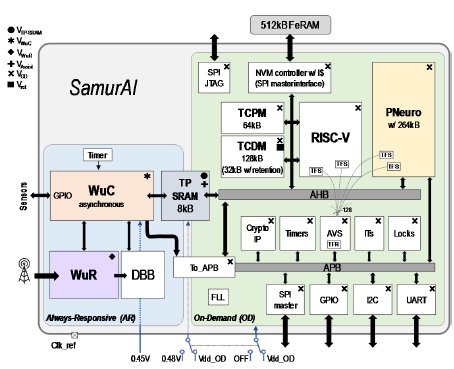

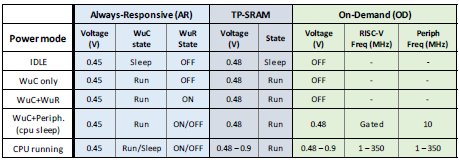

An event-driven IoT node is a way to reduce the power consumption of sporadic computing. SamurAI (Fig. 1) combines an event-driven WuC using asynchronous logic (low-energy, clock-less, and fast wake-up time) in the AR subsystem with an energy efficient synchronous RISC-V CPU including specialized accelerators in the OD sub-system to make a versatile IoT node. Depending on the application needs, one or both cores can be used as shown in Fig. 2.

Fig. 1: SamurAI system architecture, with Always-Responsive and On-Demand sub-systems and associated power domains.

Fig. 2: SamurAI power modes.

Related Semiconductor IP

- ReRAM NVM in DB HiTek 130nm BCD

- UFS 5.0 Host Controller IP

- PDM Receiver/PDM-to-PCM Converter

- Voltage and Temperature Sensor with integrated ADC - GlobalFoundries® 22FDX®

- 8MHz / 40MHz Pierce Oscillator - X-FAB XT018-0.18µm

Related Articles

- ioPUF+: A PUF Based on I/O Pull-Up/Down Resistors for Secret Key Generation in IoT Nodes

- Taking on the 130nm node and beyond

- Using a Versatile, Independent IP Platform for SoC Design

- Scaling NAND flash to 20-nm node and beyond

Latest Articles

- Quantifying Uncertainty in FMEDA Safety Metrics: An Error Propagation Approach for Enhanced ASIC Verification

- SoK: From Silicon to Netlist and Beyond Two Decades of Hardware Reverse Engineering Research

- An FPGA-Based SoC Architecture with a RISC-V Controller for Energy-Efficient Temporal-Coding Spiking Neural Networks

- Enabling RISC-V Vector Code Generation in MLIR through Custom xDSL Lowerings

- A Scalable Open-Source QEC System with Sub-Microsecond Decoding-Feedback Latency