Growing demand for high-speed data in consumer devices gives rise to new generation of low-end FPGAs

By Jason Zhu, CEO, GOWIN Semiconductor

When a designer of telecoms equipment such as a server or switch specifies an FPGA for a high-speed data interfacing function, performance is the most important criterion for choosing the preferred device. If the rule of thumb in specifying an electronics component is that the designer can have one or two of high speed, low power consumption, small size and low cost, but not three or all four of these attributes, the telecoms equipment manufacturer will prioritize high speed above the other factors.

This has given the manufacturers of high-end, high-density FPGAs a strong incentive to develop products which are packed with high-performance SerDes capabilities, and which support the high-speed communications protocols – PCIe, Ethernet, Infiniband and so on – on which communications service providers’ fiber networks are based.

These FPGAs might be large, they might be expensive, and they might be power-hungry – but this is of little importance to equipment manufacturers serving the telecoms market, as long as they are fast.

How different it is in the market for portable and wearable consumer devices, where the cost, power consumption and size of an FPGA are impossible to overlook. This has meant that the FPGA’s role in consumer devices has generally been limited to functions which basic FPGAs – small, low-power, low-density and low-cost products – can perform, such as:

- Glue logic integration

- Simple counter

- Basic state machine

- Control logic

- I/O and interface bridging

- I/O expansion

- Aggregation of multiple sensor inputs

- Voltage monitoring

For anything more demanding, the FPGA market did not in the past provide products which could meet the consumer market’s speed/cost/size requirements.

In fact, there was no demand for the FPGA’s high-speed data interfacing capabilities for as long as consumer devices were handling relatively small amounts of data to support undemanding input and output devices such as a basic camera or a small display.

But the consumer world is changing: technology and consumer demand are driving data throughput off the scale. We are discovering that there is almost no limit to people’s appetite for vivid, ultra high-definition (UHD) video and AI-enhanced high-resolution imaging, even in space- and power-deprived wearable products such as AR/VR headsets and smart glasses (see Figure 1).

For instance, a VR headset will typically be required to cram the type of UHD content more normally viewed on a large TV screen on to two synchronized displays. Not only must the output achieve 4K or even 8K resolution, it must also be rendered at a higher frame rate – typically 128 frames/s – than a standard TV achieves, to avoid the risk of motion blur.

Fig. 1: to create immersive experiences, a VR headset requires ultra high-definition display capability, and the internal data bandwidth to support it

This is leading device manufacturers to migrate from interfaces such as MIPI D-PHY or DisplayPort for video to higher-speed alternatives such as MIPI C-PHY. And this calls for the type of high-speed SerDes capability that the telecoms equipment designer uses an FPGA to provide.

But we know that the high-speed FPGAs developed for the telecoms market are not suitable for consumer devices.

This is why I foresee the emergence of a new category of FPGA at the low-density, low-cost end of the market that has previously been limited to basic logic functions.

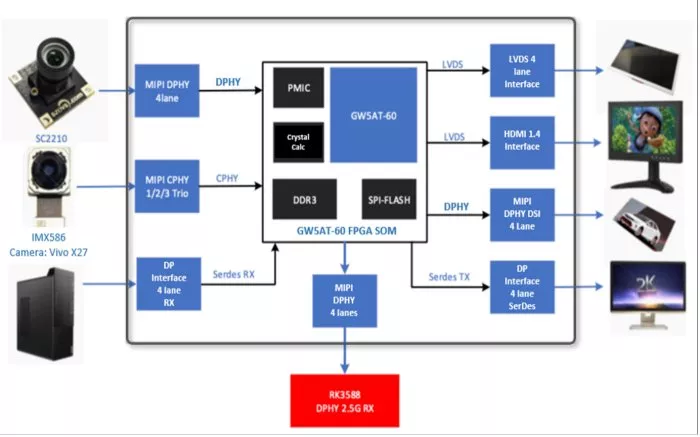

This new-generation FPGA will be optimized for high-speed SerDes functions: it will offer not only raw high-speed SerDes capability, but will also specifically support the protocols that the new consumer devices is using, such as MIPI C-PHY and PCIe, either as soft-coded IP or even hard-coded into the silicon (see Figure 2). This SerDes capability will be backed by more generous provision of high-speed memory than is usual in low-end FPGAs.

Fig. 2: examples of video bridging and processing use cases in the latest consumer devices

Optimized for data-interfacing and data-bridging functions, this new generation of FPGA will provide limited scope for implementing other logic functions, with few general-purpose logic elements available to the application, in order to minimize die size and cost.

GOWIN Semiconductor’s view is that such an FPGA demands a strategic shift from the manufacturers of low-density FPGAs. To date, they have met the requirement for low cost by stretching out the life of legacy process nodes used to fabricate their products, using a 40nm process or older, for which the investment in equipment and mask sets is relatively small.

GOWIN itself has a strong position in consumer devices with its LittleBee family of low-density FPGAs, which are themselves built on a legacy process. The LittleBee FPGAs perform a data aggregation function in many wearable and mobile devices. Without data aggregation, sensor data would be transferred to the main microcontroller or system-on-chip (SoC), and commands or configuration data transferred from the SoC to sensors, over low-speed interfaces such as I2C, UART or SPI working as sideband communication channels. This results in the proliferation of wires between the SoC and sensor sub-systems, which are often mounted on a separate board from the main controller board.

By implementing data aggregation in an FPGA, data from multiple sensors can be combined into a single high-speed data stream, reducing the number of physical network connections between the host and the various sub-systems. An example of the implementation of data aggregation is the OCP DC-SCM project in servers.

While legacy fabrication processes might be adequate for the aggregation of low-speed I2C, UART or SPI interfaces, however, they are not going to meet the requirement for advanced SerDes circuitry: the MIPI C-PHY specification, for instance, supports a data rate of up to 13.7Gbps [1], offering as much as three times the bandwidth of the earlier MIPI D-PHY standard.

This is why GOWIN took the radical decision to move to an advanced node – a TSMC 22nm ultra low-power process – for its Arora V family of low-density FPGAs. This 22nm process has allowed GOWIN to include a high-speed transceiver on-chip in the Arora V FPGAs. It has also enabled much larger memory provision: in the shift from the 55nm node used for LittleBee FPGAs to 22nm, the size of the memory cell shrinks by 90%.

The practical consequence of the decision to adopt 22nm fabrication can be seen in the specifications of the Arora V GW5AT-60 product. It features four transceivers supporting a data-rate range of 270Mbps up to 12.5Gbps. A hardcore MIPI D-PHY interface offers four data lanes, and a hardcore MIPI C-PHY has three data lanes. Softcore interfaces include PCIe 2.0 (with 1, 2 and 4 lanes), and LVDS at up to 1.25Gbps, as well as a DDR3 interface operating at up to 1,333Mbps. Memory provision includes 118 blocks of 2,124kb block SRAM, and 468kb of shadow SRAM. The FPGA also includes 60k LUT4 logic elements. The device’s core voltage is 0.9V/1.0V/1.2V.

This illustrates the way that, by fabricating at an advanced node, it becomes possible to create a low-density, low-power FPGA that provides for very high-speed data interfacing. And because of the small size of this FPGA, it can be offered at a unit cost which is affordable in wearable and portable consumer devices. In fact, the cost is attractive enough that OEMs can retain the FPGA in high-volume production, without having to contemplate replacing it with a custom ASIC, a step which is time consuming and risky, and which OEMs prefer to avoid.

The commitment to an advanced silicon process in a product family which includes low-end FPGAs is now pointing the market in a new direction, one which combines the high-speed transceiver capabilities of traditional telecoms FPGAs with the low cost and low power consumption of traditional low-end FPGAs.

There is a ready market for this new generation of FPGAs in consumer devices which use new high-speed transceiver capabilities to meet the needs, today, of ultra high-definition cameras and displays – and in future, potentially of additional high-speed peripherals supporting a new set of features and use cases driven by AI, AR and VR systems.

Reference:

[1] MIPI C-PHY maximum data rate, from: https://www.mipi.org/specifications/c-phy

Related Semiconductor IP

Related Articles

- Paving the way for the next generation of audio codec for True Wireless Stereo (TWS) applications - PART 5 : Cutting time to market in a safe and timely manner

- MIPI in next generation of AI IoT devices at the edge

- The role of IP in the new generation of data center SoCs

- Enabling a new generation of connected devices

Latest Articles

- SNAP-V: A RISC-V SoC with Configurable Neuromorphic Acceleration for Small-Scale Spiking Neural Networks

- An FPGA Implementation of Displacement Vector Search for Intra Pattern Copy in JPEG XS

- A Persistent-State Dataflow Accelerator for Memory-Bound Linear Attention Decode on FPGA

- VMXDOTP: A RISC-V Vector ISA Extension for Efficient Microscaling (MX) Format Acceleration

- PDF: PUF-based DNN Fingerprinting for Knowledge Distillation Traceability