One Platform, Five Libraries: Certus Semiconductor’s I/O IP Portfolio for Every Application on TSMC 22nm ULL/ULP Technologies

By Certus Semiconductor

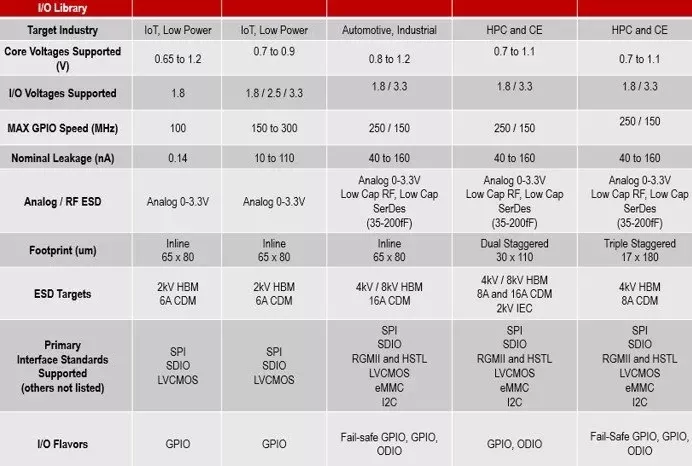

Certus Semiconductor’s I/O libraries for TSMC’s 22nm ultra-low leakage (22ULL) and 22nm ultra-low power (22ULP) technologies offer robust, high-performance solutions tailored to a wide range of SoC designs — from ultra-low power IoT nodes to demanding consumer and automotive systems. Whether you need low leakage, high drive strength, or analog compatibility, our production-proven IP covers it all. The portfolio includes:

- Ultra-low power I/O library featuring a 1.8V General Purpose Input Output (GPIO)

- Ultra-low leakage, high-speed flip-chip I/O library featuring 1.8V to 3.3V GPIO

- The Inline I/O library includes a 1.8V to 3.3V GPIO, Fail-Safe GPIO and Open-Drain Input Output (ODIO)

- The Dual Staggered I/O library includes 1.8V to 3.3V GPIO with 5V ODIO

- The Triple Staggered I/O library includes 1.8V to 3.3V Fail-Safe GPIO Library

All five are implemented and verified in TSMC’s 22ULL/ULP processes, providing an ideal combination of performance, leakage, and density for today’s advanced node designs.

Ultra-low power I/O library featuring a 1.8V GPIO

Designed for ultra-low power edge applications, this library runs on TSMC 22ULL/ULP and supports core voltages from 0.65 V to 1.2 V, with a fixed 1.8 V I/O rail. With leakage as low as 0.14 nA, this ultra-low power library is a standout choice for battery-powered wearables and IoT systems. GPIO speeds reach 100 MHz, supporting interfaces like SPI, SDIO and base LVCMOS compatibility. Its inline 65 µm x 80 µm footprint makes it pad ring–friendly, while 2 kV HBM / 6 A CDM ESD protection and 3.3 V analog tolerance provide solid protection without extra area.

Ultra-low leakage, high-speed flip-chip I/O library featuring 1.8V to 3.3V GPIO

Built for multi-voltage flexibility in TSMC 22ULL/ULP, this library supports core voltages from 0.7 V to 0.9 V and I/O levels at 1.8 V, 2.5 V, and 3.3 V. With leakage ranging from 10 to 110 nA and GPIO speeds from 150 MHz to 300 MHz, this library enables high-speed digital I/O and legacy I/O support within one library. It maintains the same inline 65 µm x 80 µm layout as the library above and is ESD hardened to 2 kV HBM / 6 A CDM. Analog I/O is supported up to 3.3 V, and interface coverage includes SPI, SDIO and base LVCMOS compatibility, making it perfect for configurable I/O subsystems in mixed-signal SoCs.

Inline I/O library including a 1.8V to 3.3V GPIO, Fail-Safe GPIO and ODIO

This library is the go-to library on TSMC 22nm ULL/ULP for industrial and automotive-grade designs. It supports 0.8 V to 1.2 V core, with 1.8 V and 3.3 V I/O levels and delivers GPIO speeds of 250 MHz (1.8 V) and 150 MHz (3.3 V). Leakage falls between 40 and 160 nA, while robust ESD protection hits 4 kV / 8 kV HBM and 16 A CDM, meeting AEC-Q100 standards. This inline library maintains a compact inline 65 µm x 80 µm footprint and supports SPI, SDIO, RGMII, HSTL, LVCMOS, eMMC, and I2C, as well as analog input capability up to 3.3 V. Ideal for use in harsh environments or over molded packages. Included are low capacitance RF pads with less than 120fF and 200fF targeting 4kV and 8kV ESD protection, including bond pad.

Dual Staggered I/O Library featuring a 1.8V to 3.3V GPIO with 5V ODIO

On TSMC 22ULL/ULP, this library supports core voltages from 0.7 V to 1.1 V, and 1.8 V / 3.3 V I/O voltages, with leakage in the 40–160 nA range. Both libraries reach 250 MHz (1.8 V) / 150 MHz (3.3 V) GPIO performance and are built for consumer and HPC markets with interfaces like SPI, SDIO, RGMII, HSTL, eMMC, I2C, and LVCMOS. This library has an inline or dual staggered option.

- Inline option features a 65 µm x 80 µm footprint, easing layout reuse with OG22.

- Dual Staggered option features 30 µm x 110 µm footprint for higher density and current handling. It includes 2 kV IEC system-level protection, plus 4 kV / 8 kV HBM and 8 A / 16 A CDM. Both provide analog and RF ESD support up to 3.3 V, and low-cap SerDes interfaces (35–200 fF), enabling high-speed links.

Triple Staggered I/O library featuring a 1.8V to 3.3V Fail-Safe GPIO Library

This triple-staggered library is Certus’s most flexible offering on TSMC 22ULL/ULP, supporting 0.7 V to 1.1 V core voltages, 1.8 V and 3.3 V I/O, and up to 250 MHz GPIO speeds. It enables level shifting and isolation between voltage domains using three separate supplies: VDD, VDDIO, and VREF. Leakage remains within 40–160 nA, while ESD protection hits 4 kV HBM / 8 A CDM.

The triple-staggered 17 µm x 180 µm footprint maximizes pad density for pin-limited SoCs. Like the above offering, it includes analog and RF ESD up to 3.3 V, along with low-cap SerDes support (35–200 fF) for high-speed differential signals.

Tailored for TSMC 22ULL/ULP — and for You

All five libraries are verified by our customers in TSMC 22ULL/ULP and are supported by Certus’s customization services to help you hit performance, leakage, ESD, and area targets. Whether you're integrating into a mixed-signal chip, building a multi-rail SoC, or designing for automotive-grade reliability, Certus has the IP and expertise to match.

Let’s engineer I/O solutions that accelerate your tapeout – and elevate your product.

Related Semiconductor IP

- 1.8V/3.3V GPIO Library with HDMI, Aanlog & LVDS Cells in TSMC 22nm

- Ultra-low leakage I/O Library in TSMC 22nm

- Three-Speed Inline Library with Open Drain I/0 in TSMC 22nm

- Ultra-low leakage I/O Library in TSMC 22nm

- Very fast VMAF accelerator

Related White Papers

- Structural netlist efficiently verifies analog IP

- Analog IP verification guidelines

- Leverage always-on voice trigger IP to reach ultra-low power consumption in voice-controlled devices

- Hitless I/O: Overcoming challenges in high availability systems

Latest White Papers

- CSR Management: Life Beyond Spreadsheets

- One Platform, Five Libraries: Certus Semiconductor’s I/O IP Portfolio for Every Application on TSMC 22nm ULL/ULP Technologies

- Get More Reliable Automotive ICs with a Shift Left Design Approach

- Evaluating Lossless Data Compression Algorithms and Cores

- How to design secure SoCs, Part III: Secure Boot