An Outline of the Semiconductor Chip Design Flow

By Ambuj Nandanwar, Softnautics

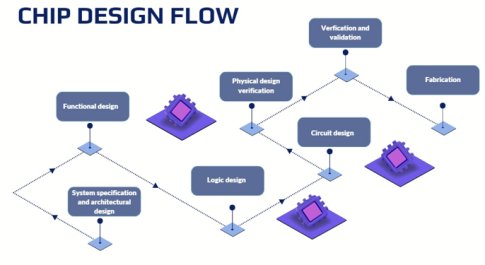

The process of chip design is a complex and multi-step endeavour that involves various stages from initial system specifications to manufacturing. Each step is crucial in achieving the goal of producing a fully operational chip. This article provides an overview of the chip design flow, its different stages, and their contributions toward creating an effective chip. These stages include system specifications, architectural design, functional design, logic design, circuit design, physical design verification, and manufacturing.

The first step in any new development involves determining the type of device/product to be designed, such as an integrated circuit (IC), ASIC, FPGA, SoC, and others. For instance, if the aim is to create something small yet powerful enough for high-speed applications like telecommunications or networking equipment, the best option might be an Application-Specific Integrated Circuit (ASIC). If the goal is to design something more flexible, capable of performing multiple tasks with minimal overhead, then an FPGA could be a better choice. Once the device type is chosen, the specifications can be defined.

Concept of chip design

A chip is a small electronic device that is programmed to perform a specific function. These devices are used in various applications, including computers and cell phones. VLSI technology has revolutionized the electronics industry by enabling designers to integrate millions or even billions of transistors onto a single chip. This has led to the development of powerful processors, memory devices, and other advanced electronic systems.

Chips are designed using different types of technology depending on their application requirements. Let us look into the flow of the entire chip design process.

- System specification and architectural design

The first step in the chip design flow is to define the requirements and specifications of the chip. This includes defining what your product will do, how it will be used, and what performance metrics you need to meet. Once these requirements are defined, they can be used as input into designing your architecture and layout.

The next step in chip design after establishing the requirements is to create an architecture that meets them while keeping costs and power consumption to a minimum, among other considerations. During the initial phase of chip design, designers make crucial decisions about the architecture, such as choosing between RISC (Reduced Instruction Set Computer) or CISC (Complex Instruction Set Computer), determining the number of ALUs (Arithmetic Logic Units) required, deciding on the structure and number of pipelines, selecting cache size, and other factors. These choices form the foundation of the rest of the design process, so it is vital that designers carefully evaluate each aspect and consider how it will impact the chip's overall efficiency and performance. These decisions are based on the chip's intended use and defined requirements, with the ultimate goal of creating a design that is efficient and effective while minimizing power consumption and costs. After completing the architectural design phase, designers create a Micro-Architectural Specification (MAS), which is a written description of the chip's architecture. This specification allows designers to accurately predict the design's performance, power consumption, and die size. By creating a comprehensive MAS, designers can ensure that the chip meets the requirements and specifications established during the initial design phase. A thorough MAS is critical to avoid errors later in the process and to ensure that the chip design meets the required performance standards and timelines. This may involve choosing between different processor types or FPGAs (Field-Programmable Gate Arrays).

Chip design flow

- Functional design

Next in the process is functional design. It involves defining the functionality and behavior of the chip. This includes creating a high-level description of the system's requirements and designing the algorithms and data flow needed to meet those requirements. The goal of this stage is to create a functional specification that can be used as a blueprint for the rest of the design process.

- Logic design

This step involves the creation of the digital logic circuits required to implement the functionality defined in the functional design stage. This stage includes creating a logical design using a hardware description language (HDL) and verifying the design's correctness using simulations.

- Circuit design

This stage involves designing the physical circuitry of the chip, including the selection of transistors, resistors, capacitors, and other components. The circuit design stage also involves designing the power supply and clock distribution networks for the chip.

- Physical design verification

Physical design verification is the process of checking the physical layout of a chip. This involves identifying any design issues and ensuring that the chip will be manufactured correctly. In this step, design of integrated circuit layout is verified via EDA software tools like logic simulators, logic analyzers, etc. and various techniques such as Design Rule Check (DRC), Layout versus Schematic (LVS), and timing and power analysis to ensure correct electrical and logical functionality and manufacturability.

- Verification and validation

Once you have completed the design of your chip, it is time to test it. This is called verification and validation (V&V). V&V involves testing the chip using various emulation and simulation platforms to ensure that it meets all the requirements and functions correctly. If there are any errors in the design, it will show up during this stage of development. Validation also helps identify the functional correctness of few initially manufactured prototypes.

At last is the fabrication of physical layout design. After the chip is designed and verified, a .GDS file is sent to foundry for fabrication.

Each stage of the chip design flow is critical to creating a successful and functional chip. By understanding the requirements of each stage, chip designers can create efficient, reliable, and cost-effective designs that meet the need of their customers across various industrial domains.

Future of chip design

The future of chip design is exciting and rapidly evolving, as technology advances. Next-gen chipsets enable new-age solutions by offering higher performance, lower power consumption, and increased functionality. These advancements drive innovation across many industries. One example of next-gen chipsets enabling new-age solutions is Artificial Intelligence (AI) and Machine Learning (ML) applications. AI and ML require significant computational power, which is possible with advanced chipsets. These technologies are used to create autonomous vehicles, personalized healthcare solutions, and advanced robotics, among others.

Another area where next-gen chipsets are making a significant impact is the Internet of Things (IoT) space. The proliferation of connected devices requires powerful, energy-efficient, and cost-effective chipsets to enable communication and data processing across a wide range of devices. Next-gen chipsets are also driving advancements in 5G networks, which are expected to deliver high-speed, low-latency connectivity and unlock new possibilities in areas such as virtual reality, augmented reality, and remote surgery.

The future of chip design is bright, and next-gen chipsets will enable more innovative solutions across many industries. As technology evolves, we can expect even more exciting developments in chip design and the solutions they enable.

To conclude, the process of chip design is complex and comprises several steps and stages, which has a significant impact on the industry. Currently, there are various types of chips in use. As new technologies continue to emerge, there will always be opportunities for improvement in how we construct these chipsets.

Related Semiconductor IP

- ReRAM NVM in DB HiTek 130nm BCD

- UFS 5.0 Host Controller IP

- PDM Receiver/PDM-to-PCM Converter

- Voltage and Temperature Sensor with integrated ADC - GlobalFoundries® 22FDX®

- 8MHz / 40MHz Pierce Oscillator - X-FAB XT018-0.18µm

Related Articles

- Differentiation Through the Chip Design and Verification Flow

- An Automated Flow for Reset Connectivity Checks in Complex SoCs having Multiple Power Domains

- Paving the way for the next generation of audio codec for True Wireless Stereo (TWS) applications - PART 5 : Cutting time to market in a safe and timely manner

- AI, and the Real Capacity Crisis in Chip Design

Latest Articles

- An FPGA-Based SoC Architecture with a RISC-V Controller for Energy-Efficient Temporal-Coding Spiking Neural Networks

- Enabling RISC-V Vector Code Generation in MLIR through Custom xDSL Lowerings

- A Scalable Open-Source QEC System with Sub-Microsecond Decoding-Feedback Latency

- SNAP-V: A RISC-V SoC with Configurable Neuromorphic Acceleration for Small-Scale Spiking Neural Networks

- An FPGA Implementation of Displacement Vector Search for Intra Pattern Copy in JPEG XS