Rambus Announces Tapeout and Availability of 112G Long Reach SerDes PHY on Leading-edge 7nm Node for High-Performance Communications and Data Centers

SerDes PHY delivers leading-edge performance and power efficiency for next-generation SoCs in data-intensive applications

SUNNYVALE, Calif. – April 16, 2019 – Today Rambus Inc. (NASDAQ: RMBS) announced its newest portfolio solution of 112G Long Reach (LR) SerDes PHY on a leading-edge 7nm process node for next-generation terabit switches, routers, optical transport networks (OTNs), and high-performance networking equipment. As the industry rapidly transitions to 400GB and 800GB wired communication applications, 112G is a key building block necessary to support the ever-growing demand for more bandwidth in data center and network applications, doubling the data rate of 56G SerDes. Rambus is at the forefront of implementing 112G design to address the long-reach backplane requirements for next-generation data-intensive applications.

This high-speed PHY provides the optimal combination of power efficiency, performance and area, adding to Rambus’ leading-edge large portfolio of silicon-proven intellectual property (IP), design tools and reference flows. With the introduction of 112G, this technology achieves higher performance to rapidly enable industry infrastructure for the 400GB and 800GB applications.

“By leveraging leading 7nm process technology, Rambus is enabling the next generation of Communications and Data Center applications,” said Hemant Dhulla, VP and GM of IP Cores, Rambus. “We’re excited to continue to expand our IP portfolio and deliver our customers top-of-the-line performance and flexibility for today’s most challenging systems, including solutions like our 112G LR SerDes PHY.”

This latest portfolio addition highlights Rambus leadership in high-speed SerDes PHY IP, leveraging the company’s long tradition of signal and power integrity expertise — remaining at the forefront of innovation in interface technology.

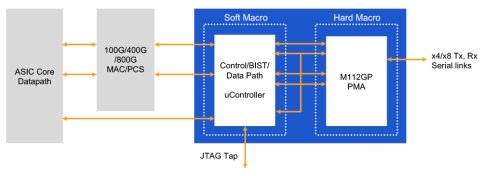

Rambus 112G Long Reach SerDes PHY

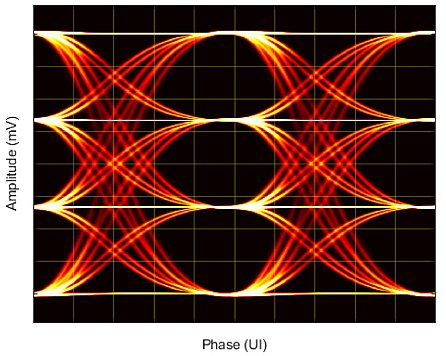

Rambus Modeled PAM-4 Signaling Transmit Eye

Technical Details

The will deliver enterprise-class performance across the demanding backplane environments beyond 30dB. To achieve this data rate requires an innovative SerDes architecture approach to meet the ever-growing data needs for high-speed data-intensive applications.

Key features of the Rambus 112G LR SerDes PHY include:

- Scalable ADC-based (analog-to-digital converter) architecture with support for PAM-4 and NRZ signaling

- DSP-based architecture for improved signal to noise ratio (SNR) and extended reach

- Configurable to provide power, performance and area (PPA) optimization for medium reach (MR) and long reach (LR) applications.

Availability and Additional Information

The Rambus 112G LR SerDes PHY is currently available for licensing and early access design customers can engage today.

With a near-term roadmap featuring industry-leading 112G solutions for extreme short reach (XSR), the Rambus industry-standard interface offerings are high-quality, complete PHY solutions designed with a system-oriented approach to maximize flexibility in today’s most challenging system environments. For more information on our latest high-speed SerDes PHY portfolio offerings, please visit rambus.com/serdes.

Related Semiconductor IP

- Die-to-Die, 112G Ultra-Extra Short Reach PHY Ported to TSMC N7 X16, North/South (vertical) poly orientation

- Die-to-Die, 112G Ultra-Extra Short Reach PHY Ported to TSMC N6 X16, North/South (vertical) poly orientation

- Die-to-Die, 112G Ultra-Extra Short Reach PHY Ported to TSMC N5 X16, North/South (vertical) poly orientation

- Die-to-Die, 112G Ultra-Extra Short Reach PHY Ported to TSMC N5 X8, North/South (vertical) poly orientation

- Die-to-Die, 112G Ultra-Extra Short Reach PHY Ported to TSMC 12FFC X8, North/South (vertical) poly orientation

Related News

- MediaTek Delivers 112G Long Range SerDes IP, Silicon-Proven on 7nm for ASIC Services

- Cadence Accelerates Next-Generation Cloud Datacenter Infrastructure with Industry's First Silicon-Proven, Long-Reach 7nm 112G SerDes IP

- Credo First to Publicly Demonstrate 112G SerDes in 7nm at TSMC's 2018 China OIP Forum

- Credo First to Demonstrate 7nm, 112G XSR SerDes

Latest News

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems

- QuickLogic Appoints Quantum Leap Solutions as Authorized Sales Representative

- Cadence and NVIDIA Expand Partnership to Reinvent Engineering for the Age of AI and Accelerated Computing

- Cadence and Google Collaborate to Scale AI-Driven Chip Design with ChipStack AI Super Agent on Google Cloud