PCI-SIG® Announces PCI Express® 8.0 Specification to Reach 256.0 GT/s

The upcoming PCIe® specification is targeted for release by 2028

SANTA CLARA, Calif.-- August 5, 2025 -- PCI-SIG® today announced the PCI Express® (PCIe®) 8.0 specification will double the data of the PCIe 7.0 specification to 256.0 GT/s and is planned for release to members by 2028.

PCI-SIG technical workgroups will be developing the PCIe 8.0 specification with the following feature objectives:

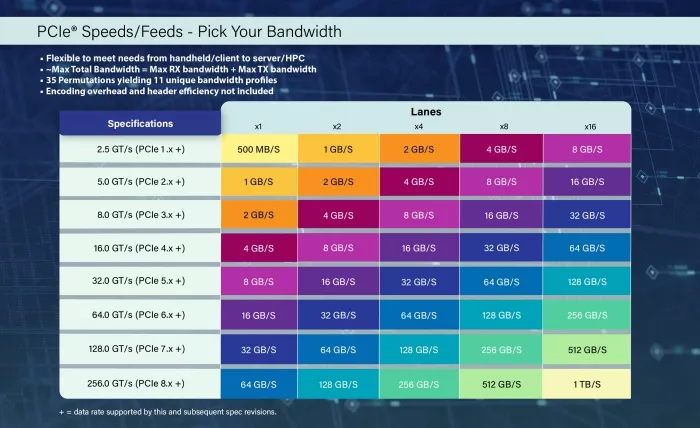

- Delivering 256.0 GT/s raw bit rate and up to 1 TB/s bi-directionally via x16 configuration

- Reviewing new connector technology

- Confirming latency and FEC targets will be achieved

- Ensuring reliability targets are met

- Maintaining backwards compatibility with previous generations of PCIe technology

- Developing protocol enhancements to improve bandwidth

- Continuing to emphasize techniques to reduce power

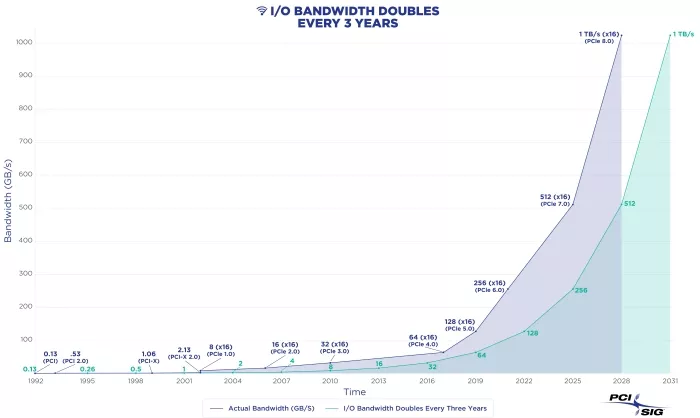

PCIe I/O bandwidth doubles every 3 years

“Following this year’s release of the PCIe 7.0 specification, PCI-SIG is excited to announce that the PCIe 8.0 specification will double the data rate to 256 GT/s, maintaining our tradition of doubling bandwidth every three years to support next-generation applications,” said Al Yanes, PCI-SIG President and Chairperson. “With the increasing data throughput required in AI and other applications, there remains a strong demand for high performance. PCIe technology will continue to deliver a cost-effective, high-bandwidth, and low-latency I/O interconnect to meet industry needs.”

“As artificial intelligence and other data-intensive applications continue to scale rapidly, PCIe technology demand will be sustained in the long run due to its high bandwidth, scalability and power efficiency,” said Reece Hayden, Principal Analyst, ABI Research. “Data center networks are already preparing to implement PCIe 6.0 technology and are showing great interest in the PCIe 7.0 specification. The introduction of the PCIe 8.0 specification further ensures that the industry’s bandwidth requirements will be supported well into the future.”

The PCIe 8.0 specification is aimed at supporting emerging applications like Artificial Intelligence/Machine Learning, high-speed networking, Edge computing and Quantum computing; and data-intensive markets like automotive, hyperscale data centers, high-performance computing (HPC) and military/aerospace.

PCIe technology is flexible to meet bandwidth needs from handheld/client to server/HPC.

About PCI-SIG

PCI-SIG is the consortium that owns and manages PCI specifications as open industry standards. The organization defines industry standard I/O (input/output) specifications consistent with the needs of its members. Currently, PCI-SIG is comprised of 1,000 industry-leading member companies. To join PCI-SIG, and for a list of the Board of Directors, visit www.pcisig.com.

Related Semiconductor IP

- AXI Bridge with DMA for PCIe IP Core

- PCIe Gen 7 Verification IP

- PCIe Gen 6 Phy

- PCIe Gen 6 controller IP

- PCIe GEN6 PHY IP

Related News

- PCI-SIG Publishes PCI Express 4.0, Revision 0.9 Specification

- PCI-SIG Achieves 32GT/s with New PCI Express 5.0 Specification

- PCI-SIG Announces Upcoming PCI Express 6.0 Specification to Reach 64 GT/s

- Cadence Announces New Low-Power IP for PCI Express 5.0 Specification on TSMC N5 Process

Latest News

- Analog Bits Demonstrates Real-Time On-Chip Power Sensing and Delivery on TSMC N2P Process at TSMC 2026 Technology Symposiums

- TES offers a High-Frequency Synthesizer and Clock Generator IP for X-FAB XT018 - 0.18µm BCD-on-SOI technology

- Faraday Delivers IP Solutions to Enable Endpoint AI Based on UMC’s 28nm SST eFlash

- AiM Future Partners with Metsakuur Company to Commercialize NPU-Integrated Hardware

- ESD Alliance Reports Electronic System Design Industry Posts $5.5 Billion in Revenue in Q4 2025