InCore Unveils SoC Generator Platform: From Idea to FPGA Validation in Minutes; Demonstrates Silicon Proof of Auto-Generated SoC

June 14, 2025 -- Chennai, India – InCore Semiconductors, a fabless semiconductor startup, today announced a major milestone with the successful silicon validation of a test chip generated using its proprietary SoC Generator platform. This breakthrough highlights a bold new future for automated chip design – where fully customized SoCs can go from concept to FPGA validation in minutes rather than weeks/months.

The Secret Sauce

At the heart of this innovation is InCore’s SoC Generator, a powerful automation platform built to radically simplify and accelerate SoC development. Traditionally, even FPGA-based prototyping of custom SoCs can take months due to the complex interplay of IP integration, interconnect design, and software readiness. InCore’s platform collapses this timeline to mere minutes – automatically generating interconnects, integrating IP, and producing all required collateral to boot software on FPGAs almost instantly.

Impact on modern chip design

“Our vision is to remove friction from early-stage SoC design,” said Neel Gala, CTO and Co-founder of InCore Semiconductors. “With our SoC Generator, an architect can go from idea to FPGA-validation in just 10 minutes. That’s a game-changer for anyone building silicon products. This enables not just rapid high confidence rototyping, but also easier design-space exploration. If I am tinkering with multiple ideas for my SoC architecture, I can just fire this tool with 10 different configurations, go for a coffee, and come back to see the results working on actual FPGA hardware, along with initial PPA landing zones.”

Democratising Chip Design

“This is more than a tool – it’s a shift in how chips will get designed in the future,” said G.S. Madhusudan, CEO and Co-founder. “By cutting down design and validation cycles from months to minutes, we’re opening the door for faster innovation, reduced costs, and broader participation in chip design.” Commenting on the current state of chip design and the need to lower the barrier to entry, he noted, “As Moore’s law grinds to a halt, ushering in an era of application-specific computing, a dramatic shift in chip design is unfolding. Historically, semiconductor giants like Nvidia, Marvel and Broadcom built their empires by crafting customized ASICs. Yet this specialization came with hefty trade-offs: hundreds of millions of dollars, thousands of engineers, and multi-year development cycles affordable only to few large companies. Today, we dare to disrupt this costly status quo, enabling small teams with SoC design superpowers that they did not have access to previously. Especially with the increasing penetration of RISC-V, even large incumbents will want to migrate their product portfolio to RISC-V quickly, and we aim to be their prime enablers with this platform.”

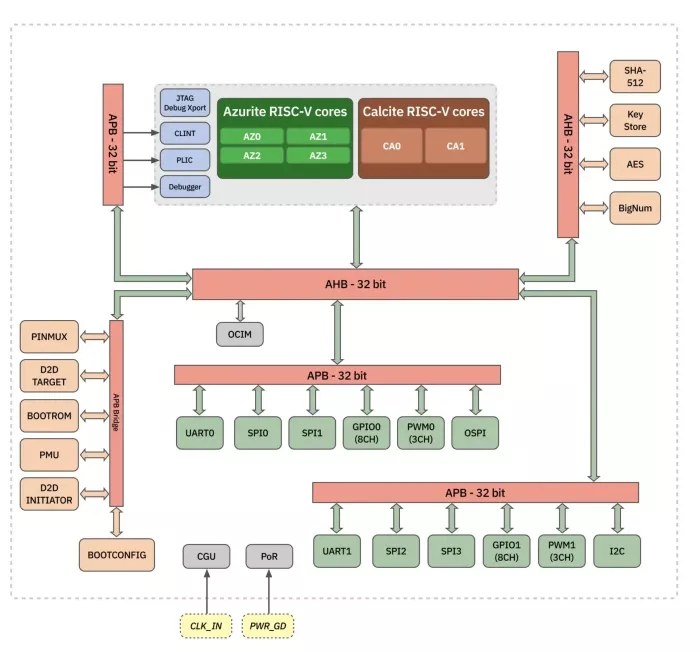

Block Diagram of InCore’s Latest Test Chip crafted using SoC Generator Platform, showcasing its ability to generate complex SoC designs instantly

Silicon Proof

InCore’s recently taped-out test chip, fabricated on TSMC’s 40nm node, serves as proof of the platform’s silicon readiness. Crafted using the SoC Generator platform, the chip integrates six heterogeneous RISC-V cores, each auto-configured and optimized using the platform, a custom in-house NoC, and several peripheral IPs (in-house and 3rd party), demonstrating the tool’s flexibility and robustness. The platform also generates the software collateral and documentation for the chip. The chip has passed successful bring-up and can run a real-time operating system (RTOS), confirming both functional and architectural soundness.

Months to Minutes

Treating the test chip’s design process as a case study, traditional methodologies would have required a team of 3-4 SoC engineers and 2-3 months to go from concept to RTL-freeze. With the SoC Generator platform, a single SoC designer was able to create the first-cut of the SoC RTL in mere minutes. After running multiple iterations to achieve optimal SoC configuration, RTL-freeze was possible in 2-3 days. Moreover, downstream teams like software, verification and physical design were able to left-shift and start work sooner, hence impacting the overall chip design timeline significantly.

To AI or not to AI

On comparison with emerging Gen-AI based chip design tools, Neel Gala said, “Our SoC Generator is about deterministic precision, not pattern-matching guesswork.” He contrasts this reliability with the uncertainty currently associated with generative AI, noting, “Chip design involves billions of possible scenarios. Mistakes aren’t merely costly – they’re catastrophic. This demands guaranteed accuracy, not probabilistic hallucinations. Hence our focus is to give our users Gen-AI-like superpowers for SoC design, but with deterministic guardrails to ensure bug-free hardware.”

Global ambitions: From Cores to full SoCs.

InCore is already a rising challenger in the global RISC-V CPU market. Customers have rigorously evaluated these CPU cores and found better PPA, customizability and support compared to incumbents, and are in the process of production rollout for chips powered by InCore IP. Now with InCore’s SoC Generator platform, scrappy chip startups are designing next-generation chips faster to race ahead of competition. InCore now plans to offer the SoC Generator platform as a standalone solution to fabless semiconductor companies and SoC teams globally, empowering them to iterate faster, explore more architectural options, and de-risk their designs before committing to tapeout. To strengthen the IP portfolio supported by SoC Generator platform, InCore is partnering with a range of diverge IP providers in win-win partnerships, starting with SmartDV.

To learn more about the SoC Generator platform or inquire about early access and licensing, visit www.incoresemi.com or contact info@incoresemi.com.

About InCore Semiconductors

InCore Semiconductors is a Chennai-based fabless semiconductor company focused on design automation and customizable RISC-V IP. A spin-out from the SHAKTI program at IIT Madras and backed by Peak XV Partners (formerly Sequoia Capital India), InCore aims to democratize custom silicon by enabling faster, automated, and accessible SoC development.

Related Semiconductor IP

- UCIe D2D Adapter & PHY Integrated IP

- Low Dropout (LDO) Regulator

- 16-Bit xSPI PSRAM PHY

- MIPI CSI-2 CSE2 Security Module

- ASIL B Compliant MIPI CSI-2 CSE2 Security Module

Related News

- Primemas Selects Achronix Embedded FPGA Technology For System-on-Chip (SoC) Hub Chiplet Platform

- VeriSilicon Launches the Industry-Leading Automotive-Grade Intelligent Driving SoC Design Platform

- Faraday Unveils FlashKit™-22RRAM: an eNVM-based SoC Development Platform for IoT

- Andes and Arculus System Collaborate to Integrate iPROfiler™ into AndeSysC, Expanding Virtual Platform Support for RISC-V SoC Design

Latest News

- Wind River Joins the CHERI Alliance and Collaborates with Innovate UK to Accelerate Cybersecurity Innovation

- Arteris and MIPS Partner to Accelerate Development for Physical AI Platforms

- DCD-SEMI expands CryptOne with EdDSA Curve25519 IP core for secure embedded systems

- Syntacore's SCR RISC-V IP Now Supports Zephyr 4.3

- Xylon Presents New 12-Channel GMSL3/GMSL2 FMC+ ExpansionBoard