Dolphin Integration announces the availability of the new generation 28 nm SpRAM generator

Grenoble, France – April 17, 2017 -- Launching any low-power SoC on a highly competitive market requires true differentiating factors. For IoT applications requiring ultra low-power solutions to extend battery life-time for wireless-connected devices, SoC architects optimize power modes by partitioning the SoC. This minimizes dynamic power in active modes, as well as power leakage in stand-by modes. Dolphin Integration is on a continuous quest to provide new solutions to their customers, to help them address their challenges.

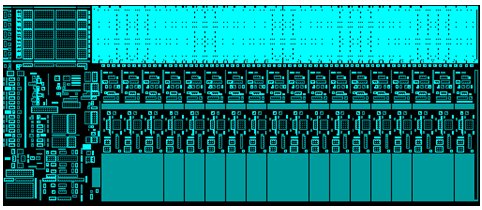

Dolphin Integration announces the availability of the Calypso architecture. Calypso is a SpRAM optimized for low-power SoCs in TSMC 28 nm HPM technology.

This Single-port SRAM is designed to optimize power consumption, with gains between 20 and 30% compared to alternative solutions in 28 nm.

Detail from a corner of Calypso SpRAM 28

The SpRAM Calypso reaches such a performance thanks to its data retention mode, with a memory core lowered to 0.63 V. This minimum voltage retention feature allows leakage to be divided by between 2 and 10 (depending on memory size) compared to other memory compilers in stand-by mode.

I want to receive information on SpRAM Calypso

SpRAM Calypso is part of a our 28 nm HPM portfolio, which includes:

- ultra high-density 6-track standard cell libraries,

- our unique cache controller, R-Stratus-LP, both improving speed and reducing power consumption by up to 3 times, compared to stand-alone eFlash memory,

- our innovative MAESTRO™, a fabric IP making the implementation of the Activity Control Unit of a low-power SoC easy and safe.

For further information on our Memories, visit our website or contact us.

About Dolphin Integration

Dolphin Integration contributes to "enabling low-power Systems-on-Chip" for worldwide customers - up to the major actors of the semiconductor industry - with high-density Silicon IP components best at low-power consumption.

"Foundation IPs" includes innovative libraries of standard cells, register files and memory generators as well as an ultra-low power cache controller. "Fabric IPs" of voltage regulators, Power Island Construction Kit and their control network MAESTRO™ enable to safely implement low-power SoCs with the smallest silicon area. They also star the "Feature IP": from ultra-low power Voice Activity Detector with high-resolution converters for audio and measurement applications to power-optimized 8 or 16 and 32 bit micro-controllers.

Over 30 years of experience in the integration of silicon IP components, providing services for ASIC/SoC design and fabrication with its own EDA solutions, make Dolphin Integration a genuine one-stop shop addressing all customers' needs for specific requests.

It is not just one more supplier of Technology, but the provider of the Dolphin Integration know-how!

Related Semiconductor IP

- Single Port High-Speed Multi Bank SRAM Memory Compiler on GF 22FDX+

- Single Port High Speed SRAM Memory Compiler on N22ULL

- Single Port Low Voltage SRAM Memory Compiler on N22ULL - Low Power Retention and Column Repair

- Single Port Low Voltage SRAM Memory Compiler on N22ULL

- Single Port Low Leakage SRAM Memory Compiler on GF 22FDX+

Related News

- Dolphin Integration breakthrough innovation for TSMC 180 nm BCD Gen 2 process: Up to 30% savings in silicon area with the new SpRAM RHEA

- Dolphin Integration announces the availability of the new generation of Foundry Sponsored SpRAM generator at 55 nm

- Dolphin Integration announces the availability of the new generation of SpRAM generator at 90 nm and 55 nm eFlash

- Dolphin Integration sets up a large range of sponsored IPs at 55 nm to reduce SoC power consumption by up to 70%

Latest News

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems

- QuickLogic Appoints Quantum Leap Solutions as Authorized Sales Representative

- Cadence and NVIDIA Expand Partnership to Reinvent Engineering for the Age of AI and Accelerated Computing

- Cadence and Google Collaborate to Scale AI-Driven Chip Design with ChipStack AI Super Agent on Google Cloud