SoCs Get a Helping Hand from AI Platform FlexGen

By Gary Hilson, EETimes | March 21, 2025

FlexGen, a network-on-chip (NoC) interconnect IP, is aiming to accelerate SoC creation by leveraging AI.

FlexGen, a network-on-chip (NoC) interconnect IP, is aiming to accelerate SoC creation by leveraging AI.

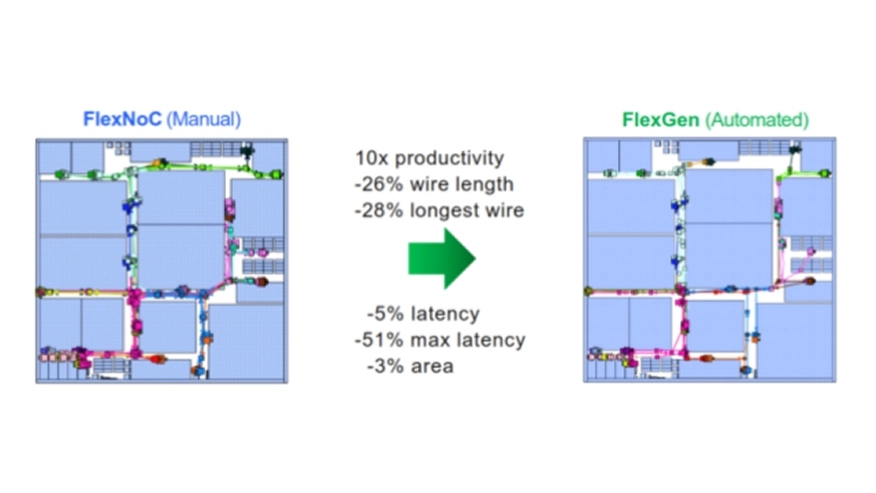

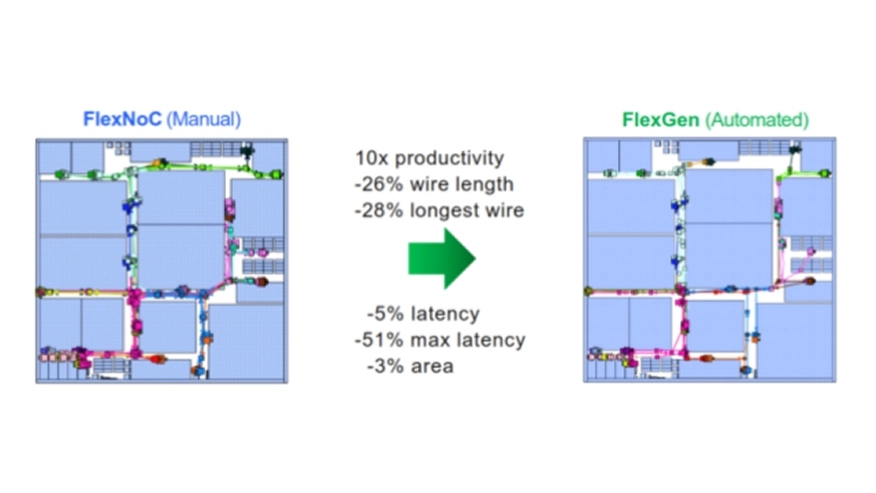

Developed by Arteris Inc., FlexGen promises to deliver a 10× productivity boost while reducing design iterations and the time required to develop. In a briefing with EE Times, Arteris CMO Michal Siwinski said FlexGen achieves up to a 30% reduction in wire length to lower power use, as well as up to 10% reduction in latency that results in improved performance in SoC and chiplet designs.

“It will actually do the process of generating that network on chip, generating that interconnect and it will actually generate however many interconnects are required to meet the requirement,” Siwinski said.

Using AI and machine learning for chip design isn’t new, Siwinski said, but often the productivity boosts come at the cost of performance or power. FlexGen is able to reduce the number of elements on the critical path of a project, while also improving power/performance metrics, which he said is unique.

To read the full article, click here

Related Semiconductor IP

- Smart Network-on-Chip (NoC) IP

- Network-on-Chip (NoC)

- NoC Verification IP

- NoC System IP

- Non-Coherent Network-on-Chip (NOC)

Related News

- Arteris Deployed by Menta for Edge AI Chiplet Platform

- Arteris Revolutionizes Semiconductor Design with FlexGen – Smart Network-on-Chip IP Delivering Unprecedented Productivity Improvements and Quality of Results

- Arteris To Provide FlexGen Smart NoC IP In Next-Generation AMD AI Chiplet Designs

- Rivian Unveils Custom Silicon, Next-Gen Autonomy Platform, and Deep AI Integration

Latest News

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems

- QuickLogic Appoints Quantum Leap Solutions as Authorized Sales Representative

- Cadence and NVIDIA Expand Partnership to Reinvent Engineering for the Age of AI and Accelerated Computing

- Cadence and Google Collaborate to Scale AI-Driven Chip Design with ChipStack AI Super Agent on Google Cloud