AI Drives PCIe Aspirations

By Gary Hilson, EETimes (September 29, 2025)

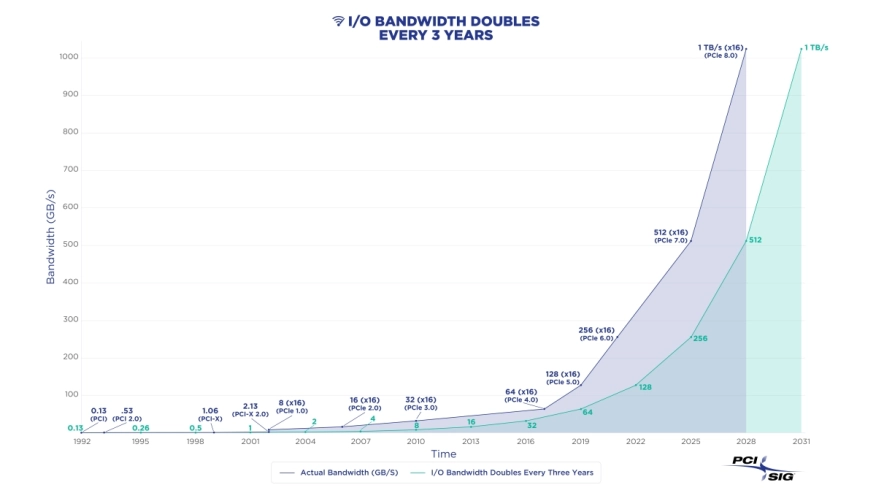

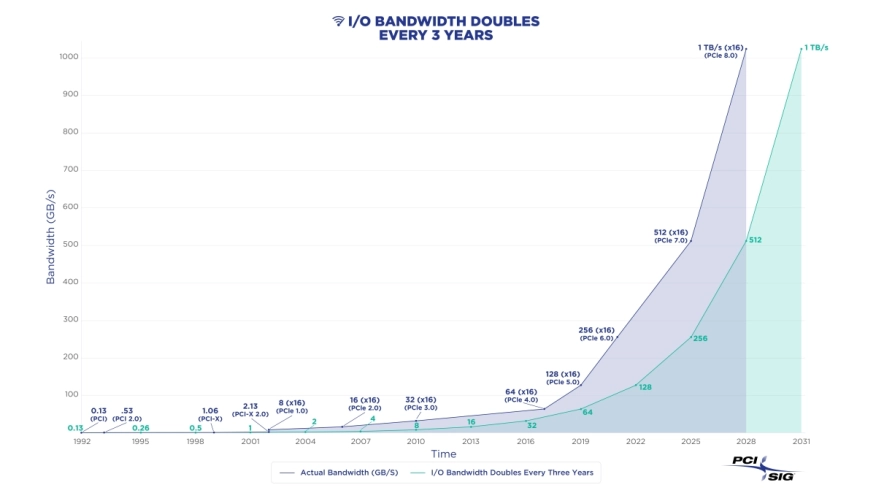

As PCIe 8.0 aims to double the data rate yet again with its 2028 release, the PCI-SIG may also need to reconsider whether backwards compatibility as far back as 1.0 is feasible.

As PCIe 8.0 aims to double the data rate yet again with its 2028 release, the PCI-SIG may also need to reconsider whether backwards compatibility as far back as 1.0 is feasible.

The aim for the next iteration of PCIe is to achieve a raw bit rate of 256.0 GT/s and up to 1 TB/s, delivered bi-directionally via an x16 configuration.

PCIe 7.0, released earlier this year, targets data-driven applications such as artificial intelligence (AI) /machine learning, 800G Ethernet, cloud computing, and quantum computing. Key features included a 128.0 GT/s raw bit rate and up to 512 GB/s bi-directionally via x16 configuration, utilizing Pulse Amplitude Modulation with four levels (PAM4) and Flit-Based encoding, as well as improved power efficiency.

To read the full article, click here

Related Semiconductor IP

- PCIe PHY and controller solution

- PCIe Controller

- PCIe 4.0 Controller

- PCIe 6.0 PHY, SS SF2A x4 1.2V, N/S for Automotive, ASIL B Random, AEC-Q100 Grade 2

- PCIe PHY

Related News

- AI Drives PCie 6 Interoperability Testing

- AI Demand Drives 4Q25 Global Top 10 Foundries Revenue Up 2.6% QoQ; Samsung Gains Share and Tower Moves Up in Rankings

- AI Compute Demand Drives 44% YoY Growth for Top 10 Global Fabless IC Firms in 2025

- Actel drives up density of flash-based FPGAs

Latest News

- Mosaic SoC raises $3.8M to bring real-time spatial intelligence to every consumer device

- UMC Reports First Quarter 2026 Results

- Rambus Appoints Sumeet Gagneja as Chief Financial Officer

- SEMI Reports Worldwide Silicon Wafer Shipments Increase 13% Year-on-Year in Q1 2026

- POLYN Technology Announces Tapeout of Automotive Chip