AccelerComm Unveils Fully Integrated PUSCH Decoder to Supercharge 5G NR for Performance-Critical Channels

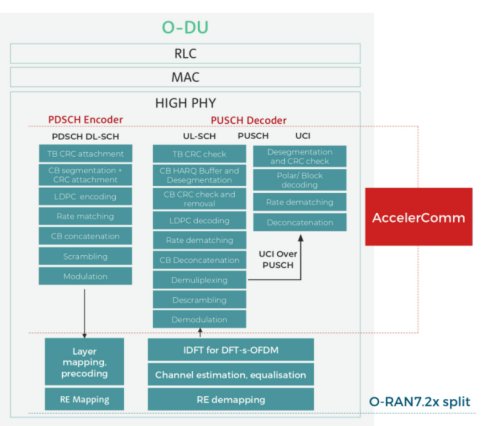

Southampton, UK and MWC Shanghai, China – February 24, 2020 -- AccelerComm, the channel coding specialist, are supercharging 5G NR with cutting edge Physical Layer IP which increases spectral efficiency and reduces latency. The company today announced a complete high-performance 5G NR PUSCH (Physical Uplink Shared Channel) Decoder and PDSCH (Physical Downlink Shared Channel) Encoder for customers who want to maximize the efficacy of their 5G radio network.

Building on the company’s carrier-grade portfolio of channel coding and modulation/ demodulation IP, this highly integrated solution enables 5G base stations to benefit from AccelerComm’s proven best-in-class LDPC decoder performance, whilst minimizing time to market.

“This product builds on the existing AccelerComm IP portfolio to enable operators to deliver on the high-performance, low-latency promise of 5G using their existing spectrum and cloud RAN infrastructure." said Robert Barnes, VP Sales & Marketing of AccelerComm.

AccelerComm’s PUSCH Decoder integrates additional 3GPP physical layer functions together with its high-performance LDPC decoders, to create a 3GPP-compliant IP package that can be quickly integrated and optimized for use in custom silicon (ASIC) and programmable hardware (FPGA).

The flexible architecture means that it can be customized depending on an operator’s service requirements, resulting in optimal performance, power, and silicon area, tailored to their specific needs.

This latest product from AccelerComm adds three new blocks of IP to complete the link between the LDPC decoder and the MIMO detector:

- gNodeB uplink stack (PUSCH Decoder)

- LDPC decoder with transport block wrapper, polar decoder, demultiplexer, descrambler and QAM demodulator

- gNodeB downlink stack (PDSCH Encoder)

- LDPC encoder with transport block wrapper, scrambler and QAM modulator

The specification is as defined in Sections 6.2 and 7.2 of 3GPP document TS 38.212, as well as Sections 6.3.1.1, 6.3.1.2, 7.3.1.1 and 7.3.1.2 of TS 38.211.

Related Semiconductor IP

Related News

- AccelerComm Announces 5G PUSCH Channel Equalizer

- AccelerComm Launches PUSCH Channel Simulator for 5G L1 Performance Evaluation

- AccelerComm® announces 5G NR NTN Physical Layer Solution that delivers over 6Gbps, 128 beams and 4,096 user connections per chipset

- National Instruments Adopts AccelerComm's 5G NR Polar IP

Latest News

- Wind River Joins the CHERI Alliance and Collaborates with Innovate UK to Accelerate Cybersecurity Innovation

- Arteris and MIPS Partner to Accelerate Development for Physical AI Platforms

- DCD-SEMI expands CryptOne with EdDSA Curve25519 IP core for secure embedded systems

- Syntacore's SCR RISC-V IP Now Supports Zephyr 4.3

- Xylon Presents New 12-Channel GMSL3/GMSL2 FMC+ ExpansionBoard