pci express IP

Filter

Compare

739

IP

from

42

vendors

(1

-

10)

-

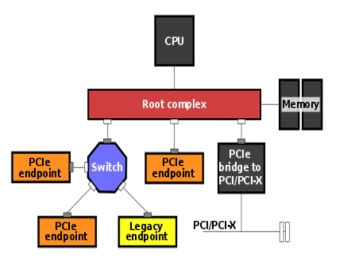

PCIe - PCI Express Controller

- The PCIe 3.0 (Peripheral Component Interconnect Express 3.0) is a computer hardware interface standard that is used to connect various components to a computer's motherboard.

- It is the third generation of the PCIe standard and offers increased bandwidth, improved performance, and reduced power consumption compared to its predecessor, PCIe 2.0 Overall, PCIe 3.0 provides faster and more efficient communication between the various components in a computer, including graphics cards, network adapters, and storage devices, resulting in better overall performance.

-

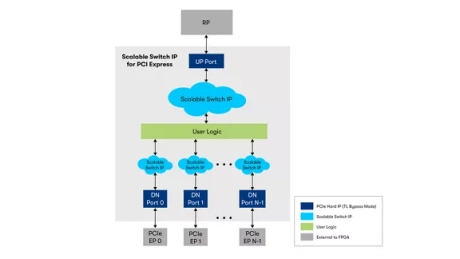

Scalable Switch Intel® FPGA IP for PCI Express

- The Scalable Switch Intel® FPGA IP for PCI Express is a fully configurable switch that implements one fully configurable upstream port and connectivity for up to 64 downstream ports.

-

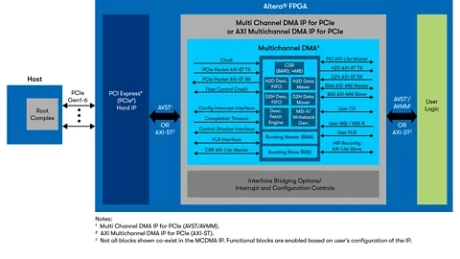

Multichannel DMA Intel FPGA IP for PCI Express*

- The Multichannel DMA IP for PCI Express provides high efficiency, speed, and configuration flexibility to support various applications from HPC, cloud, networking, to embedded

- With support for up to 2048 channels and Linux-based PCIe drivers provided, this low latency, low resource utilization solution is essential in handling movements of large volumes of data to optimize system performance.

-

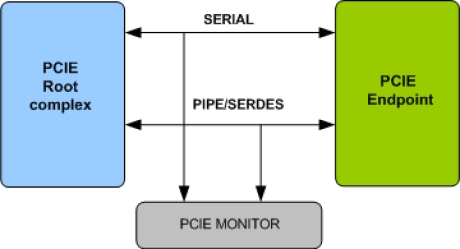

PCI Express Verification IP

- Supports PCI Express specs 1.0/2.0/2.1/3.0/4.0/5.0/6.0

- Supports mPCIe

- Supports PIPE, PCS/PMA, Message Bus and SERDES interface

- Supports MPHY RMMI and serial interface

-

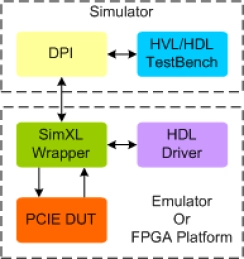

PCI Express Synthesizable Transactor

- Supports PCI Express specs 1.0/2.0/3.0/4.0/5.0/6.0.

- Supports MPCIE

- Supports PIPE, PCS/PMA, and serdes interface

- Supports MPHY RMMI and serial Interface

-

PCI Express to AMBA 4 AXI/3 AXI Bridge

- Complete IP solution consists of digital controllers, PHYs and verification IP

- Fully supports the Synopsys Controller IP for PCI Express Endpoint, Root Port, Dual Mode (EP/RP), and Switch port types

- Fully compliant with the AMBA 3 AXI and 4 AXI interconnects

- Full protocol mapping from PCI Express to the AMBA 3 AXI or 4 AXI bus protocol

-

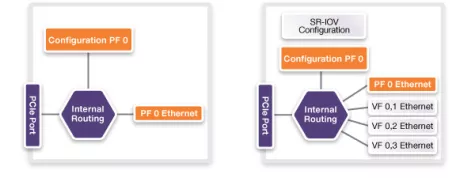

Multi-Port Switch IP for PCI Express

- Designed according to the PCI Express 4.0, 3.1, 2.1, and 1.1 specifications, including the latest errata

- Designed according to the PCI-SIG Single-Root I/O Virtualization specification

- Supports PIPE PHY interface definition including variable clock and variable data

- Supports 16.0, 8.0, 5.0 and 2.5 Gbps line rates

-

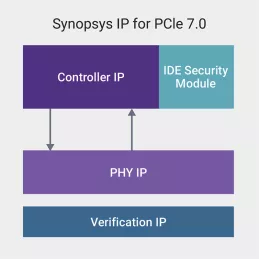

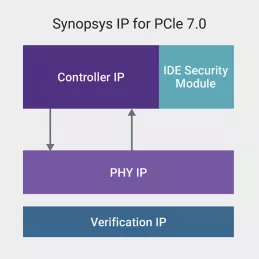

IDE Security IP Modules for PCI Express 7.0

- Full support of PCI Express 7.0 (64GT/s) IDE specification

- High-performance AES-GCM based packet encryption, decryption, authentication

- Seamless integration with Synopsys controllers via TLP/FLIT packet-based interface

- FLIT mode support

- Support for PCIe 7.0, 6.0, 5.0, 4.0 and 3.1 data rates

-

Controller IP for PCI Express 7.0

- Supports all required features of the PCI Express 7.0 (128 GT/s) specification

- Allows a full 128GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

- Advanced RAS-DES features for simplified bring-up and debug

-

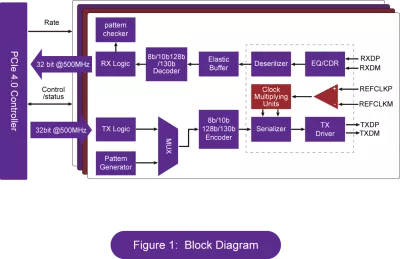

PCI Express 4.0 PHY

- Compiles with PCIe 4.0, 3.1, 2.1, 1.1 and PIPE 4.4.1 specifications

- Supports all power-saving modes (P0, P0s, P1, P2) as defined in PIPE 4.4.1 specifications

- Supports L1 PM/CPM substates with CLKREQ#

- Supports the separate REFCLK Independent SSC (SRIS) architecture