imaging vision IP

Filter

Compare

11

IP

from

7

vendors

(1

-

10)

-

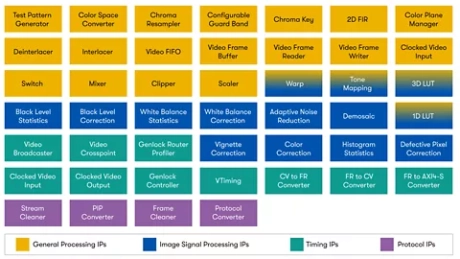

Video and Vision Processing Suite

- The Intel® FPGA Video and Vision Processing Suite is a collection of next-generation Intel® FPGA intellectual property (IP) functions that you can use to facilitate the development of custom video and image processing designs

- These Intel® FPGA IP functions are suitable for use in a wide variety of image processing and display applications, such as studio broadcast, video conferencing, AV networking, medical imaging, industrial inspections and robotics, smart city/retail and consumer.

-

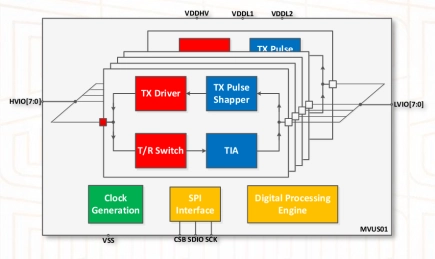

Ultrasound AFE Transceiver Chip for CMUT Transducers

- The MVUS01 ultrasound transducer interface is the first generation of high-voltage (HV) ultrasound ASICs intended for portable medical imaging probes and other markets.

- The chip supports pulsing ultrasonic transducers, with excitation voltages of up to 50V, and has high gain and low noise receivers, for increased sensitivity to ultrasonic echoes.

-

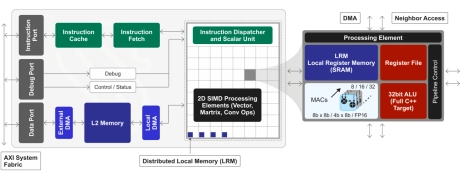

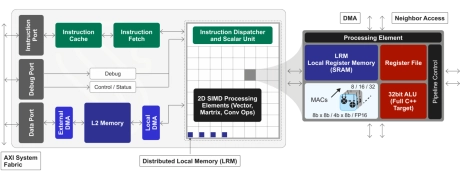

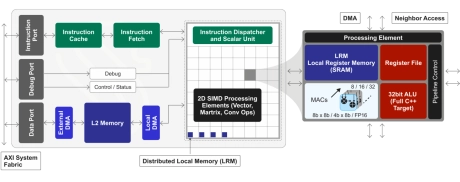

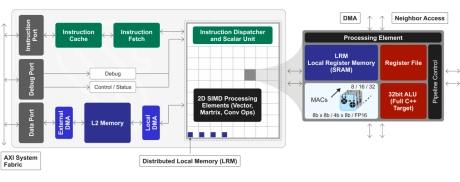

GPNPU Processor IP - 32 to 864TOPs

- 32 to 864TOPs

- (Dual, Quad, Octo Core) Up to 256K MACs

- Hybrid Von Neuman + 2D SIMD matrix architecture

- 64b Instruction word, single instruction issue per clock

- 7-stage, in-order pipeline

- Scalar / vector / matrix instructions modelessly intermixed with granular predication

-

-

-

-

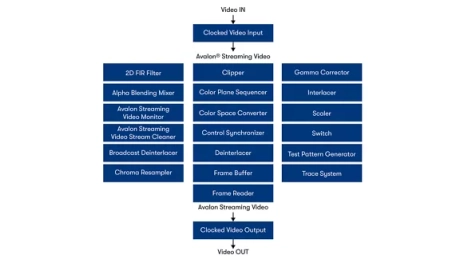

Video and Image Processing Suite

- The Intel FPGA Video and Image Processing Suite is a collection of Intel FPGA intellectual property (IP) functions that you can use to facilitate the development of custom video and image processing designs

- These Intel FPGA IP functions are suitable for use in a wide variety of image processing and display applications, such as studio broadcast, video conferencing, AV networking, medical imaging, smart city/retail, and consumer.

-

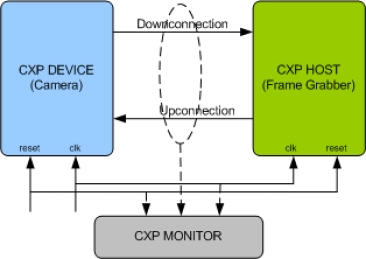

CoaXPress (CXP) Verification IP

- Full CXP Device and Host functionality.

- Supports following Channels,

- Stream Channel

- I/O Channel

-

MIPI CSI-2 IP

- The MIPI CSI-2 IP core is a highly scalable and silicon-agnostic implementation of the MIPI Camera Serial Interface 2 version 4.1 targeting ASIC and FPGA technologies.

- The MIPI CSI-2 implementation enables high-speed, low-power transmission of image data from camera modules to host processors.

-

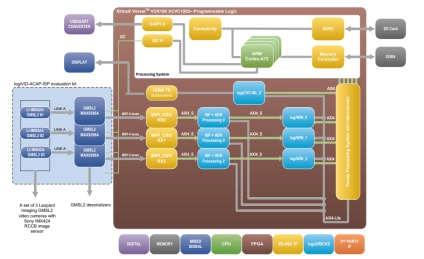

ACAP HDR Image Signal Processing Framework

- The ACAP HDR Image Signal Processing Framework is intended to showcase a complete logicBRICKS IP suite implementation of High-Dynamic Range (HDR) Image Signal Processing (ISP) pipeline in an embedded design based on AMD-Xilinx ACAP programmable devices.

- The HDR ISP pipeline enables crisp camera video under altering and rough lighting conditions in next generation multi-channel embedded systems for use in automotive, surveillance, medical, aerospace and similar video and vision AI applications.