image processing IP

Filter

Compare

242

IP

from

54

vendors

(1

-

10)

-

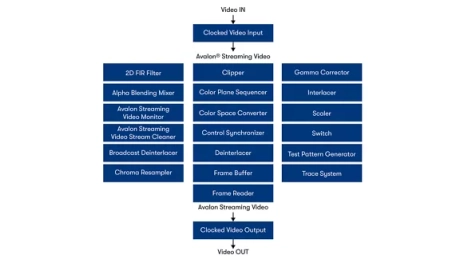

Video and Image Processing Suite

- The Intel FPGA Video and Image Processing Suite is a collection of Intel FPGA intellectual property (IP) functions that you can use to facilitate the development of custom video and image processing designs

- These Intel FPGA IP functions are suitable for use in a wide variety of image processing and display applications, such as studio broadcast, video conferencing, AV networking, medical imaging, smart city/retail, and consumer.

-

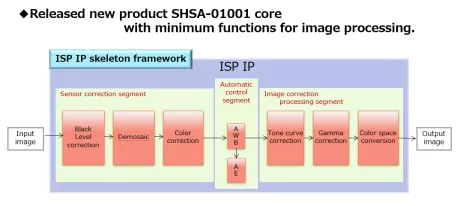

"Image Signal Processor" with the minimum functions required for image processing system

- lack Level correction/Demosaic/Color space conversion

- Auto White Balance(AWB)?Auto Exposer(AE)

- Tone curve correction/Gamma correction/Color space conversion

-

Image Signal Processor IP enabling high performance real-time image processing

- Support DVP Input Interface

- Support 8-16 Bit Bayer RAW and ITU-R BT.601 & 656 Video Interface

- Test Pattern Generator (TPG)

- Black Level Measurement and Compensation (BLS)

- Sensor Linear Correction

-

FXAFE030HH0L is an Analog Front End IP for image processing applications. FXAFE030HH0L is fabricated in UMC 40 nm logic LP/HVT Low-K process to implement a signal processing solution for scanners, video and imaging applications. _x005F_x000D_

-

Video and Image Processing Pack

- Chroma Resampler

- Color Correction

- Color Filter Array Interpolation

- Gamma Correction

-

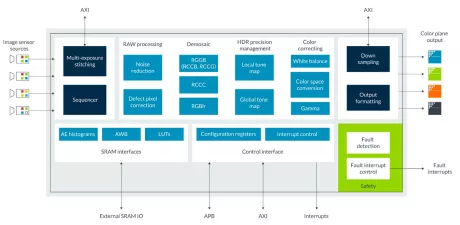

Image Signal Processor IP - High performance image signal processing for auto and industrial markets

- 32bit DVP interface, 24bit ISP pipeline

- Dual pixel per cycle throughput

- Wide Dynamic Range Tone Mapping (WDR)

- Multi-exposure HDR (Native/build in HDR, Compand output, DOL/Stagger, Stagger output)

-

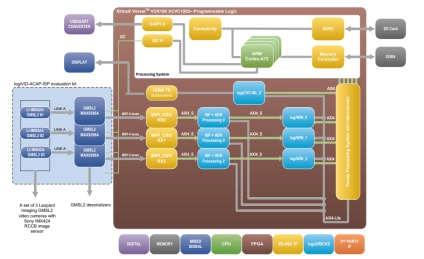

ACAP HDR Image Signal Processing Framework

- The ACAP HDR Image Signal Processing Framework is intended to showcase a complete logicBRICKS IP suite implementation of High-Dynamic Range (HDR) Image Signal Processing (ISP) pipeline in an embedded design based on AMD-Xilinx ACAP programmable devices.

- The HDR ISP pipeline enables crisp camera video under altering and rough lighting conditions in next generation multi-channel embedded systems for use in automotive, surveillance, medical, aerospace and similar video and vision AI applications.

-

Image Signal Processor IP - Ultra-low power image signal processing for AIoT and wearable markets

- Supports DVP Input Interface

- Input color formats: 8-bit, 10-bit, 12-bit Bayer; 8-bit, 10-bit YUV BT.601, BT.656; 8-bit, 10-bit monochrome

- SW Register Configuration: 32-bit AHB Slave

- Frame rate control, configurable output FPS range from 60fps to 1fps

-

Image Signal Processing for ADAS and Display Applications

- Multi-Camera Support

- Advanced Image Processing

- Every Pixel Reliable