eDP receiver IP

Filter

Compare

10

IP

from

6

vendors

(1

-

10)

-

eDP RECEIVER IIP

- Supports eDP 1.4b specification

- Supports full eDP Receiver functionality

- Supports multi lanes upto 4 lanes.

- Supports main link, Aux link and Hot plug functionality.

-

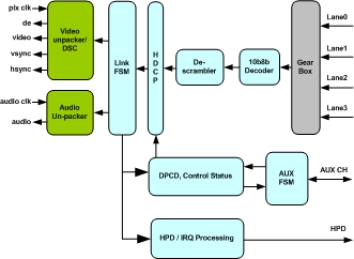

eDP 1.4 Receiver

- Compliant with Embedded DisplayPort 1.4 specification

- Support for up to 4 Dual-Speed lanes at 1.62 Gbit/s and 2.7 Gbit/s

- Supports Enhanced Framing Mode

- Integrated High-bandwidth Digital Content Protection (HDCP) version 1.4

-

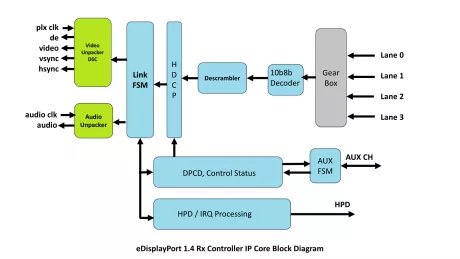

eDisplayPort v1.4 Receiver Controller IP Core

- Supports eDP 1.4b specification

- Supports full eDP Receiver functionality

- Supports multi lanes upto 4 lanes.

- Supports main link, Aux link and Hot plug functionality.

-

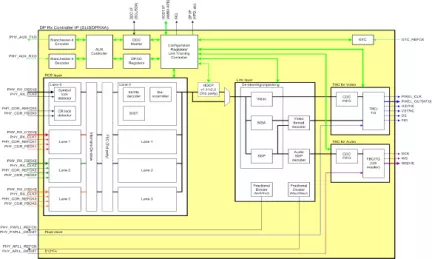

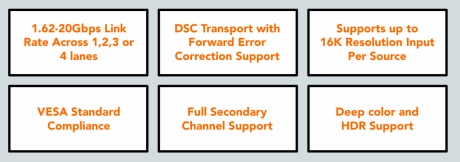

DisplayPort Receiver IP

- Silicon proven on multiple ASIC and FPGA processes

- Capable of operating without a host CPU in low complexity applications

- Horizontal and vertical video delimiter signals with 1, 2 or 4 pixels per output cycle, supporting up to 16K resolution output; deep color and HDR support

- 1.62 to 8.1 Gbps link rate across 1, 2, or 4 lanes

-

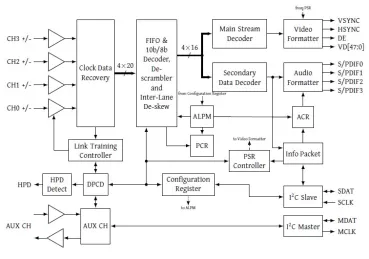

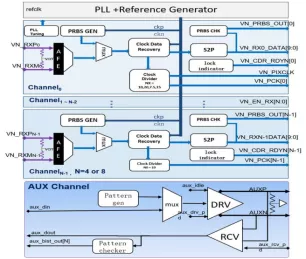

eDisplay Port v1.4 Rx PHY IP in 40LL, Silicon Proven in SMIC 40LL

- Low power operation: 22mW/lane @ typical

- Support data rate: 0.6Gbps~5.4Gbps

- Utilize 10bit parallel interface for per lane

- Independent power down control for each lane

-

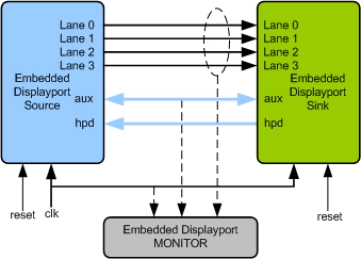

Verification IP for DisplayPort/eDP/DSC/DPI

- A comprehensive VIP solution for DisplayPort (DP) and eDP source and sink designs. DP VIP implements a complete set of models, protocol checkers and compliance testsuites in 100% native SystemVerilog and UVM .

- Comprehensive support for DP/eDP source and sink design verification.

-

Embedded Display Port Verification IP

- Full Embedded Display port source device and sink device functionality.

- Embedded Display port v1.3,1.4,1.4b and 1.5 compliant and based on display port specs 1.2/1.2a/1.3/1.4/2.0.

- Support transmitter and receiver Mode.

- Supports multi lanes upto 4 lanes.

-

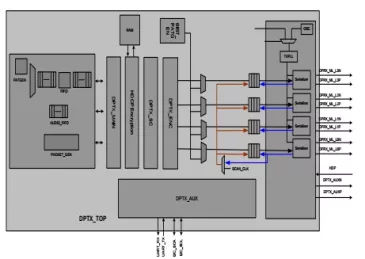

Display Port 1.2 Tx PHY & Controller IP (Silicon Proven in STMicro 28FDSOI)

- Display Port v1.2 Transmitter [1.62 - 2.7 - 5.4 Gbps/lane]

- Embedded Display Port v1.4 Transmitter

- HDMI v1.4 and Display Port v1.2 Combo receiver

- DP SST and MST compliant

-

eDP1.4/DP1.3 TX Link IP

- eDP version 1.4a, DP version 1.3 compliant receiver

- Supports HDCP Decryption

- Supports both 1.62/8.1Gbps data rate