eDP IP

Filter

Compare

46

IP

from

18

vendors

(1

-

10)

-

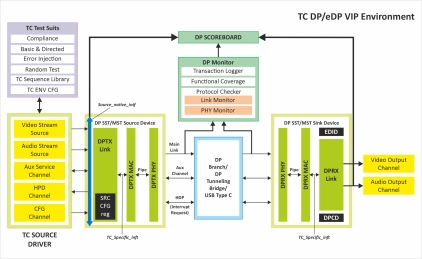

eDP 2.0 Verification IP

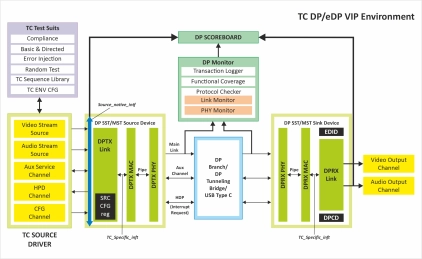

- The eDP 2.0 Verification IP provides an effective & efficient way to verify the components interfacing with the eDP interface of an ASIC/FPGA or SoC.

- The eDP VIP is fully compliant with the Standard eDP Version 2.0 specifications from VESA.

- This VIP is a lightweight VIP with an easy plug-and-play interface, so that there is no hit on the design time and the simulation time.

-

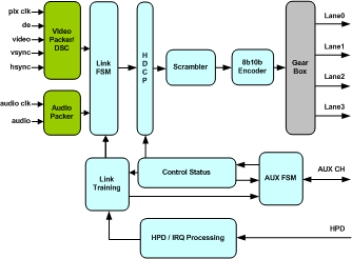

eDP TRANSMITTER IIP

- Supports eDP 1.4b specification

- Supports full eDP Transmitter functionality

- Supports multi lanes upto 4 lanes.

- Supports main link, Aux link and Hot plug functionality.

-

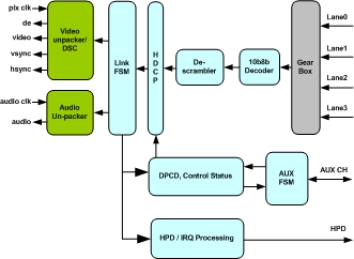

eDP RECEIVER IIP

- Supports eDP 1.4b specification

- Supports full eDP Receiver functionality

- Supports multi lanes upto 4 lanes.

- Supports main link, Aux link and Hot plug functionality.

-

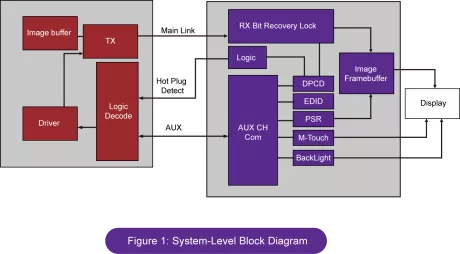

eDP 1.5 Verification IP

- Fully compliant with VESA Embedded DisplayPort (eDP) Standard 1.5 Specification

- Supports power saving feature:- Panel Self Refresh features PSR/PSR2, PR, Adaptive sync, and backlight control.

- Supports HDCP version 1.4, 2.2 and 2.3

- Supports Alternative Scrambler Seed Reset (ASSR)

- TPS4 with ASSR is supported

-

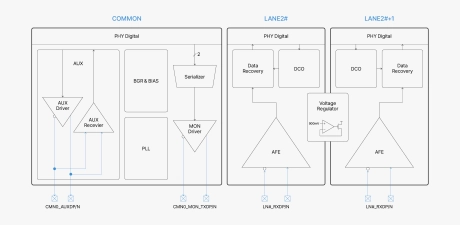

eDP PHY

- Compatible with embedded display port v1.5/v1.4b specification

- Four-lane main link with support for 8.1/5.4/4.32/3.24/2.7/2.43/2.16/1.62Gbps

- Supports Enhanced Framing Mode

- Automatic Link-Training with an option for firmware-controlled Link-Training procedure

-

eDP 1.3 Transmitter PHY

- Fully compliant to VESA Embedded DisplayPort 1.3 specifications

- Support Embedded DisplayPort RBR, HBR, and HBR2 data rate and customized data rate

- Configurable x1/x2/x4 Main-Link data lanes

- PIPE SerDes Mode interface to Embedded DisplayPort controller

-

DP and eDP TX/RX PHY IP

- eDP v1.5 compliant

- Supports for 1.62Gbps to Max 8.1Gbps data rate

- PSR, PSR2 supported for low power consumption ( FW_SLEEP, FW_STANDBY supported )

- Supports for eDP v1.5 feature such as AUX-less Link Training

-

eDP 1.4 Receiver

- Compliant with Embedded DisplayPort 1.4 specification

- Support for up to 4 Dual-Speed lanes at 1.62 Gbit/s and 2.7 Gbit/s

- Supports Enhanced Framing Mode

- Integrated High-bandwidth Digital Content Protection (HDCP) version 1.4

-

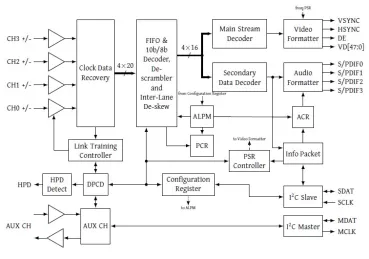

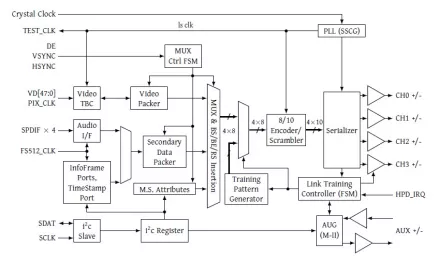

eDP 1.4 Transmitter

- Compliant with Embedded DisplayPort 1.4 specification

- Main Link supports 1, 2 or 4 lanes at 1.62Gbps, 2.7Gbps and 5.4Gbps

- 4 channel S/PDIF Digital Audio Input

- Supports Enhanced Framing Mode

-

eDP1.4/DP1.3 TX Link IP

- eDP version 1.4a, DP version 1.3 compliant receiver

- Supports HDCP Decryption

- Supports both 1.62/8.1Gbps data rate