VPU IP

Filter

Compare

15

IP

from

9

vendors

(1

-

10)

-

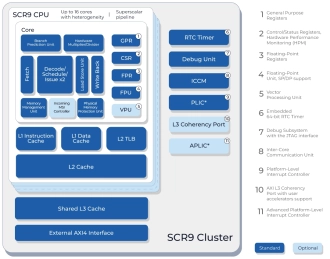

High-performance Linux-capable application core with a 12-stage dual-issue out-of-order pipeline, a VPU, cache coherency, and a hypervisor

- SCR9 is a high-performance, silicon-proven, Linux-capable 64-bit RISC-V processor core for entry-level server-class applications and personal computing devices.

- The SCR9 core supports RISC-V standard "I" Integer, "M" Integer Multiplication and Division, "A" Atomic, "C" 16-bit Compressed, "F" Single-Precision Floating-Point, "D" Double-Precision Floating-Point, "V" Vector Operations, "B" Bit Manipulation, and "K" Scalar Cryptography extensions.

-

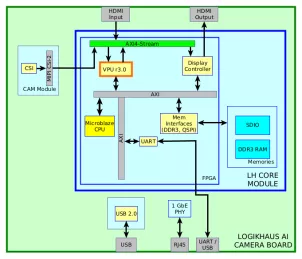

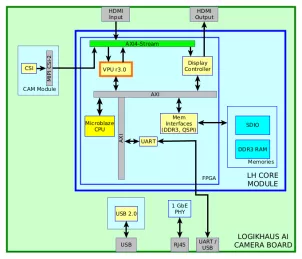

VPU R3.0 on Artix 7 100T

- Video processing system suitable for high-speed, high resolution video systems

- HDMI Full-HD (1920x1080p) input & output at 60fps

- High-speed processing at 60fps

- Uses FPGA for parallel processing

-

VPU R1.0 on Artix 7 200T

- Video processing system suitable for high-speed, high resolution video systems

- HDMI Full-HD (1920x1080p) input & output at 60fps

- High-speed processing at 60fps

- Uses FPGA for parallel processing

-

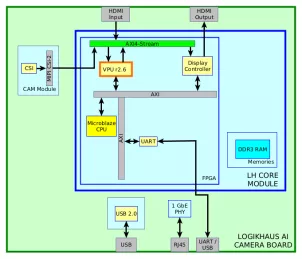

VPU R2.6 on Artix 7 200T

- Video processing system suitable for high-speed, high resolution video systems

- HDMI Full-HD (1920x1080p) input & output at 60fps

- High-speed processing at 60fps

- Uses FPGA for parallel processing

-

VPU R3.0 on Artix 7 200T

- Video processing system suitable for high-speed, high resolution video systems

- HDMI Full-HD (1920x1080p) input & output at 60fps

- High-speed processing at 60fps

- Uses FPGA for parallel processing

-

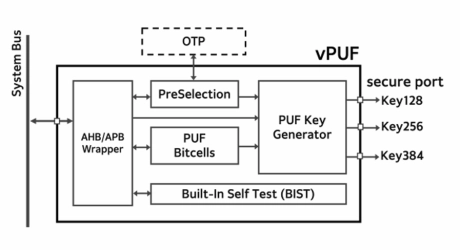

Via-PUF Security Chip for Root of Trust

-

The vPUF® IP, powered by Via PUF (Physically Unclonable Function) technology, provides a unique silicon fingerprint for inborn identity function, essential for the Root of Trust in security applications

-

-

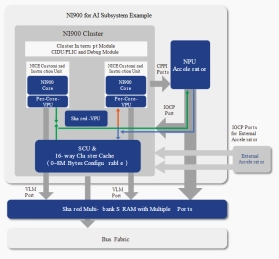

AI DSA Processor - 9-Stage Pipeline, Dual-issue

- NI900 is a DSA processor based on 900 Series.

- NI900 is optimized with features specifically targeting AI applications.

-

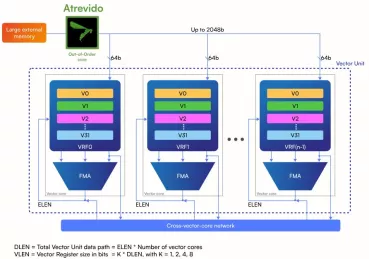

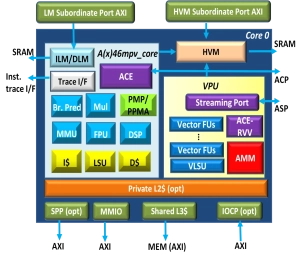

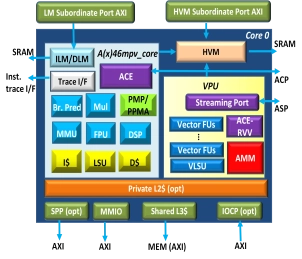

64 bit RISC-V Multicore Processor with 2048-bit VLEN and AMM

- 2 different packages with or without vector: AX46MPV, AX46MP

- in-order dual-issue 8-stage CPU core with up to 2048-bit VLEN

- Symmetric multiprocessing up to 16 cores

- Private Level-2 cache

- Shared L3 cache and coherence support

-

32 bit RISC-V Multicore Processor with 256-bit VLEN and AMM

- AndesCore™ A46MP(V) 32-bit multicore CPU IP is an 8-stage superscalar processor with Vector Processing Unit (VPU) based on AndeStar™ V5 architecture and Andes Matrix Multiply (AMM) extension.

- It supports RISC-V standard “G (IMA-FD)”, “ZC” compression, “B” bit manipulation, DSP/SIMD ‘P’ (draft), “V” (vector), CMO (cache management) extensions, Andes performance enhancements, plus Andes Custom Extension™ (ACE) for user-defined instructions.

-

Fully-custom RISC-V Vector Unit

- A Vector Unit is composed of several "Vector Cores", roughly equivalent to a GPU Core, that perform multiple calculations in parallel.

- Each Vector Core has arithmetic units capable of performing addition, subtraction, fused multiply-add, division, square root, and logic operations.