USB PHY IP

Filter

Compare

623

IP

from

42

vendors

(1

-

10)

-

USB PHY Solution

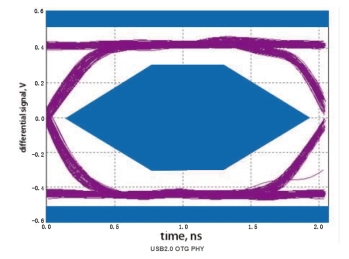

- Brite provides USB2.0 OTG PHY which is a complete mixed-signal IP solution designed to implement OTG connectivity for a System-on-Chip (SoC) design.

- The USB2.0 OTG PHY supports the USB2.0 480Mbps protocol and data rate, and is backward compatible with the USB 1.1 1.5Mbps and 12Mbps protocol and data rates.

- It has been verified by a number of end products, especially suitable for the current popular internet of things applications.

-

USB Super-speed+ PHY

- Fully compliant with USB 3.2 Gen2 specification.

- Supports data rates of 5Gbps (Gen1), 10Gbps (Gen2), and 20Gbps (Gen2x2).

- Compatible with PIPE interface:

- 8/16/32-bit at original PIPE.

-

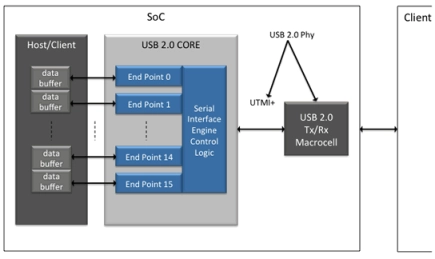

USB 2.0 PHY

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version 1.0

- Supports HS(480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- USB Data Recovery and Clock Recovery on receiving

- SYNC and EOP generation on transmit packets and detection on receive packets

-

USB 1.1 PHY, Support Low Speed and Full Speed - HLMC 55nm

- USB 1.1 PHY, Support Low Speed and Full Speed;

-

USB 1.1 PHY, Support Low Speed and Full Speed - HHGrace 110nm

- USB 1.1 PHY, Support Low Speed and Full Speed;

-

USB 2.0 PHY IP core

- Complies with USB specifications, rev. 2.0 and 1.1

- Complies with UTMI+ specification, level 3, rev. 1.0

- Supports 480Mb/s (HS), 12Mb/s (FS) and 1.5MB/s (LS) serial data transmission rates

- Supports 8-bit unidirectional Parallel Interface Engine (PIE) bus for HS, FS and LS modes, and Serial Interface Engine (SIE) for FS and LS modes

-

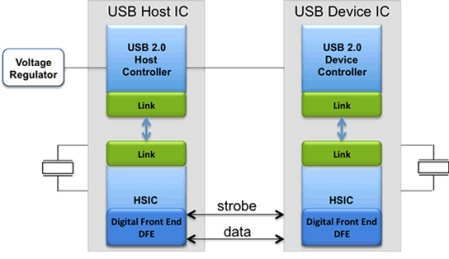

High Speed Inter-CHIP USB 2.0 PHY

- High-Speed 480Mbps data rate only

- Source-synchronous serial interface

- No power consumed unless a transfer is in progress.

- Maximum trace length of 10cm

-

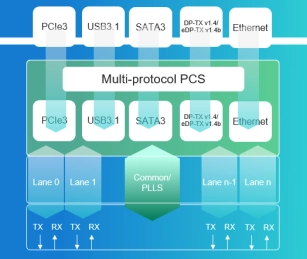

USB 3.1 PHY

- Supports USB 3.1, PCIe 3.1, DP-TX v1.4/eDP-TX v1.4b, SATA 3, 10G-KR and QSGMII/SGMII

- Multi-protocol support for simultaneous independent links

- Supports SRIS and internal SSC generation

- Supports PCIe L1 sub-states

- Automatic calibration of on-chip termination resistors

-

USB 2.0 PHY - TSMC 55ULPeF25 x1, OTG

- Ported to over 50 different processes and configurations ranging from 65-nm to 14/16-nm FinFET

- Supports the USB 2.0 protocol and data rate (480 Mbps)

- Supports the USB Type-C specification

- USB femtoPHY, USB nanoPHY and USB picoPHY offer a tunability feature that allows quick, post-silicon adjustments that occur due to process variations, or unexpected chip and board parasitic, without modifying the existing design

-

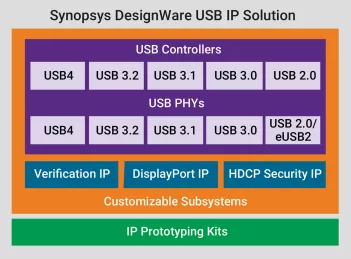

USB 3.1 PHY (10G/5G) - TSMC N5 x1 OTG, North/South Poly Orientation

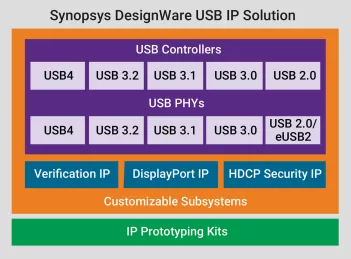

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes