USB 2.0 High Speed PHY IP

Filter

Compare

62

IP

from

15

vendors

(1

-

10)

-

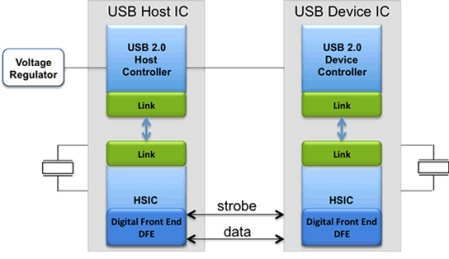

High Speed Inter-CHIP USB 2.0 PHY

- High-Speed 480Mbps data rate only

- Source-synchronous serial interface

- No power consumed unless a transfer is in progress.

- Maximum trace length of 10cm

-

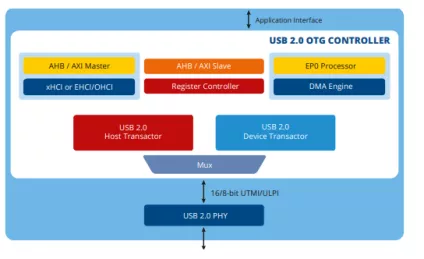

USB 2.0 OTG High / Full / Low- Speed Dual Role IP Core

- Support SW controlled host/device role switching.

- Support Fullspeed and Lowspeed

- Support Control, Bulk, Interrupt and Isochronous Transfer Types

- Support L1/L2 power saving modes for USB 2.0 port

-

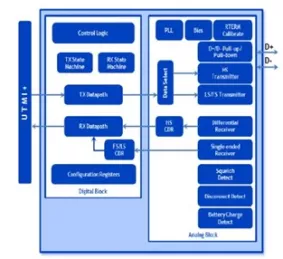

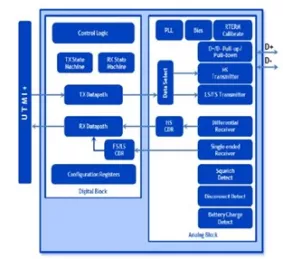

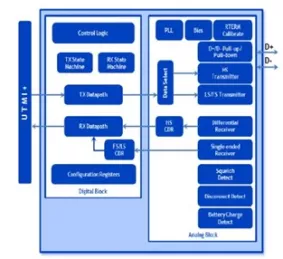

USB 2.0 PHY

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version 1.0

- Supports HS(480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- USB Data Recovery and Clock Recovery on receiving

- SYNC and EOP generation on transmit packets and detection on receive packets

-

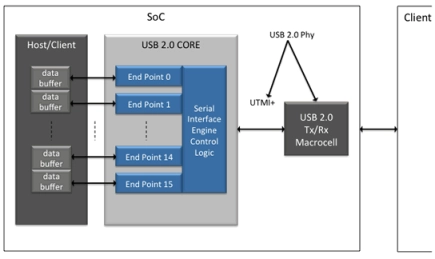

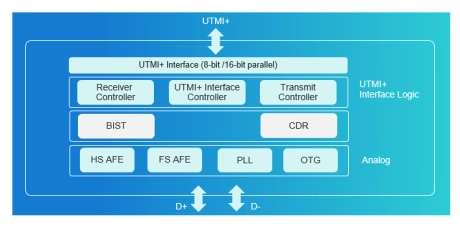

USB 2.0 PHY IP core

- Complies with USB specifications, rev. 2.0 and 1.1

- Complies with UTMI+ specification, level 3, rev. 1.0

- Supports 480Mb/s (HS), 12Mb/s (FS) and 1.5MB/s (LS) serial data transmission rates

- Supports 8-bit unidirectional Parallel Interface Engine (PIE) bus for HS, FS and LS modes, and Serial Interface Engine (SIE) for FS and LS modes

-

USB 2.0 PHY IP, Silicon Proven in TSMC 16FFC

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version level 3.

- Supports HS(480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip

-

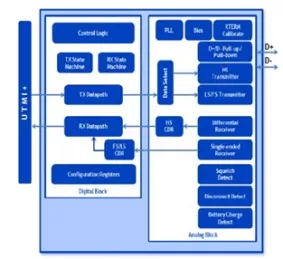

USB 2.0 PHY

- Designed to the USB 2.0 specification, and operates at High Speed (480Mbps), Full Speed (12Mbps), and Low Speed (1.5Mbps)

- Complies with the UTMI v1.05 specification

- Multiple reference clock supported from 9.6MHz up to 52MHz

- 8-bit 60MHz and 16-bit 30MHz parallel interfaces

- Battery Charging Specification v1.2

-

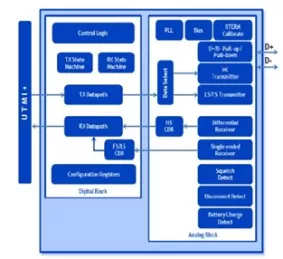

USB 2.0 PHY IP, Silicon Proven in TSMC 90G

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version level 3.

- Supports HS(480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip

-

USB 2.0 PHY IP, Silicon Proven in TSMC 65LP

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version level 3.

- Supports HS(480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip

-

USB 2.0 PHY IP, Silicon Proven in TSMC 55LP

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version level 3.

- Supports HS(480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip

-

USB 2.0 PHY IP, Silicon Proven in TSMC 12FFC

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version level 3.

- Supports HS(480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip