TCP stack IP

Filter

Compare

24

IP

from

10

vendors

(1

-

10)

-

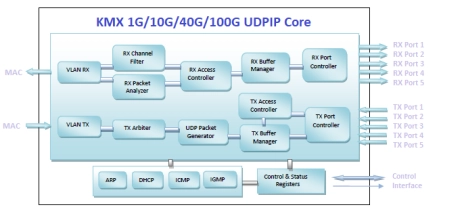

100G UDP/IP Hardware Protocol Stack Core

- The core Implements a UDP/IP hardware protocol stack that enables high-speed communication over a LAN or a point-to-point connection.

- It is ideal to offload systems from demanding tasks of UDP/IP and to enable media streaming in both FPGA and RISC designs.

- The core supports ARP request, reply and manages 32-entry ARP cache. ICMP ping reply is included.

-

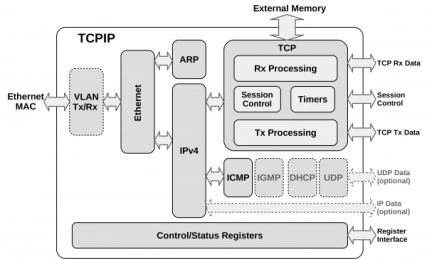

1G/10G TCP/IP Hardware Stack

- The TCPIP-1G/10G core implements a complete TCP/IP Hardware Protocol Stack.

- More capable than many offloading engines, it allows systems to connect to an Internet Protocol (IP) network and exchange data using the TCP protocol without requiring assistance from — or even the presence of — a system processor.

-

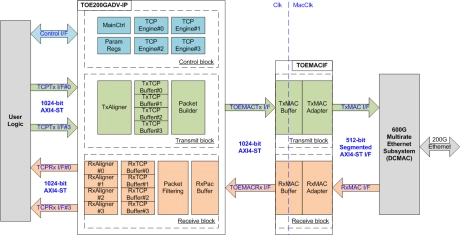

200G / 100G / 40G / 25G / 10G / 1G TCP Offloading Engine

- The TCP Offloading Engine IP core (TOE200G/100G/40G/25G/10G/1G-IP) is the epochal solution implemented without CPU.

- Generally, TCP processing is so complicated that expensive high-end CPU is required.

- TOE-IP core series built by pure hardwired logic can take place of such extra CPU for TCP protocol management.

-

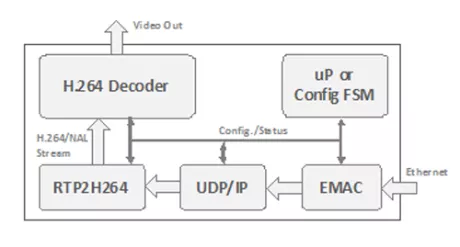

Hardware RTP Stack for H.264 Stream Decapsulation

- Implements a Real Time Transport Protocol (RTP) hardware stack that extracts H.264/NAL streams encapsulated in RTP packets.

- The RTP2H264 core is compatible with RTP packets produced by CAST’s H.264 to RTP encapsulation core (H2642RTP).

- The output of the RTP2H264 can be directly connected to the input of an H.264 decoder core.

-

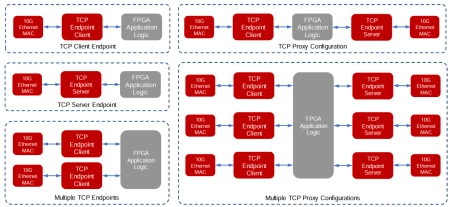

Ultra Low Latency 10G TCP Endpoint

- The TCP Endpoint implements a full, reliable streaming network stack in FPGA logic.

- It allows applications in logic to be directly connected to Internet Protocol (IP) interfaces by opening, maintaining, and closing TCP Connections via Ethernet to other hardware or software endpoints.

-

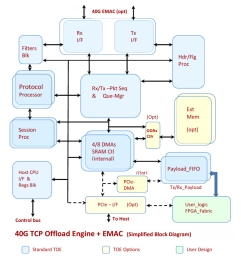

40G-1K Sess. TCP + UDP Offload Engine

- Highly customizable hardware IP block. Easily portable to ASIC flow, Xilinx/Altera FPGAs or Structured/ASIC flow.

- Eighth Generation TOE and System Solutions provide ‘Ultra-Low Latency’ and Ultra-High Performance with highest TCP bandwidth in Full Duplex. Network Tested and mature TCP protocol offload implementation

- All stages of Full TCP stack implemented in High performance hardware

-

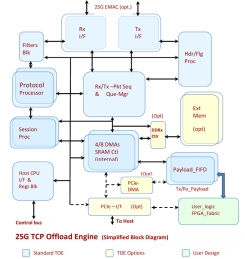

25G-1K Sess. TCP + UDP Offload Engine

- Highly customizable hardware IP block. Easily portable to ASIC flow, Xilinx/Altera

- FPGAs or Structured/ASIC flow.

- Eighth Generation TOE and System Solutions provide ‘Ultra-Low Latency’ and Ultra-High Performance with highest TCP bandwidth in Full Duplex. Network Tested and mature TCP protocol offload implementation

- All stages of Full TCP stack implemented in High performance hardware

-

-

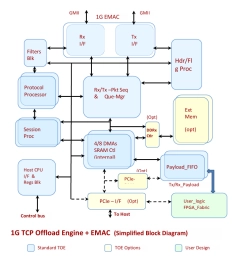

1G TCP Offload Engine TOE+MAC+Host_IF Ultra-Low Latency (STOE)

- INT 1011 is the only SOC IP Core that implements a full 1G bit TCP Stack in Handcrafted, Ultra Low Latency and Very High Performance, Innovative, Flexible and Scalable architecture which can also be easily customized for end product differentiation.

- INT 2011 is the only SOC that integrates 1G TOE + 1 GEMAC + Host interfaces in the smallest logic footprint. It is highly flexible that is customizable for layer-3, layer 4-7 network infrastructure and network security systems applications.

-

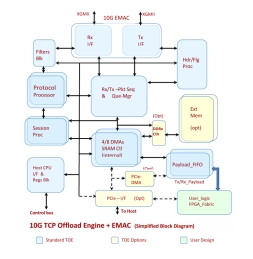

10 G bit TCP Offload Engine + PCIe/DMA SOC IP

- Highly customizable hardware IP block. Easily portable to ASIC flow, Xilinx/Altera FPGAs or Structured/ASIC flow.

- Fourth Generation TOE and System Solutions provide ‘Ultra-Low Latency’ and Ultra-High Performance with highest TCP bandwidth in Full Duplex. Network Tested and TCP protocol proven.