TCP/IP Hardware Stack IP

Filter

Compare

18

IP

from

7

vendors

(1

-

10)

-

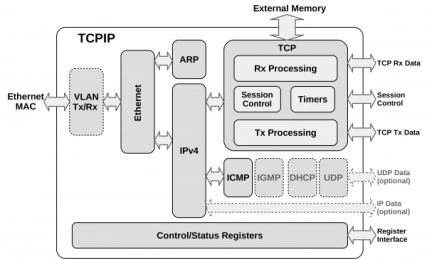

1G/10G TCP/IP Hardware Stack

- The TCPIP-1G/10G core implements a complete TCP/IP Hardware Protocol Stack.

- More capable than many offloading engines, it allows systems to connect to an Internet Protocol (IP) network and exchange data using the TCP protocol without requiring assistance from — or even the presence of — a system processor.

-

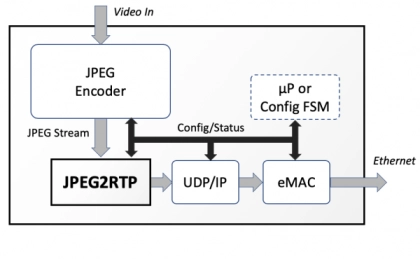

Hardware RTP Stack for JPEG Stream Encapsulation

- Implements a Real Time Transport Protocol (RTP) hardware stack that encapsulates JPEG streams to RTP packets compliant with RFC 2435.

- The JPEG2RTP can be directly connected to the output of a JPEG encoder to output RTP packets, which can subsequently be forwarded for UDP/IP or TCP/IP encapsulation.

-

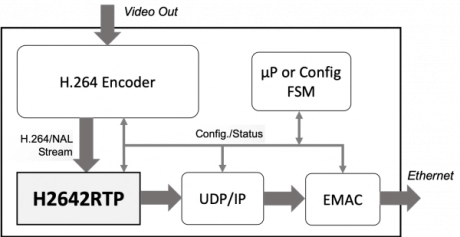

Hardware RTP Stack for H.264 Stream Encapsulation

- Implements a Real Time Transport Protocol (RTP) hardware stack that encapsulates H.264/NAL streams to RTP packets that are compliant with RFC 3894 and RFC 6184.

- The H2642RTP can be directly connected to the output of an H.264 encoder to output RTP packets, which can subsequently be forwarded for UDP/IP or TCP/IP encapsulation.

-

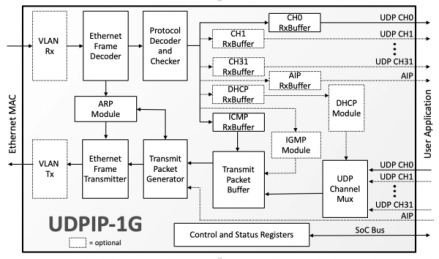

UDP/IP Hardware Protocol Stack

- Implements a UDP/IP hardware protocol stack that enables high-speed communication over a LAN or a point-to-point connection.

- Designed for standalone operation, the core is ideal for offloading the host processor from the demanding task of UDP/IP encapsulation and enables media streaming with speeds up to 1 or 10Gbps, depending on the speed of the silicon fabric, even in processor-less SoC designs.

-

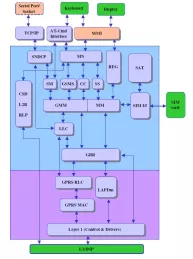

GSM GPRS EDGE Protocol Stack SW IP

- Class B implementation multi-slot class 12 to 3GPP Release 1999 June 2007

- GPRS PDP context. Packet services accessed via integrated TCP/ IP stack, or via PPP using an external PC or PDA.

- Conforms to 3GPP Release ’99 / GCF-CC v3.35 bis (GCF-CC Version 3.35.0 dated 2009-07-06) and NAPRD.03 v5.0 bis (PTCRB NAPRD.03 v5.0) based on STAR-Let200Q M2M platform

- Data rates to 80Kbps (GPRS); 400Kbps (EGPRS)

-

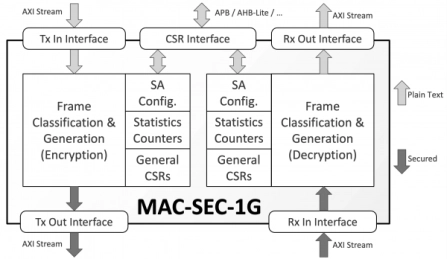

MACsec Protocol Engine for 10/100/1000 Ethernet

- The MAC-SEC-1G IP core implements a compact and configurable custom-hardware protocol engine for the IEEE 802.1AE (MACsec) standard.

- It supports all cipher suites provisioned by the MACsec standard and the VLAN-in-Clear improvement and is silicon- and performance-optimized for networks operating up to 1Gbps.

-

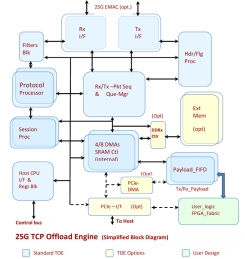

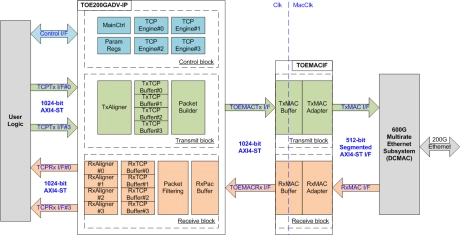

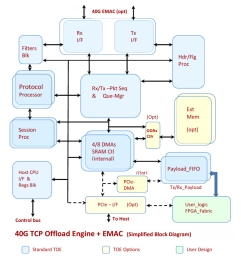

200G / 100G / 40G / 25G / 10G / 1G TCP Offloading Engine

- The TCP Offloading Engine IP core (TOE200G/100G/40G/25G/10G/1G-IP) is the epochal solution implemented without CPU.

- Generally, TCP processing is so complicated that expensive high-end CPU is required.

- TOE-IP core series built by pure hardwired logic can take place of such extra CPU for TCP protocol management.

-

-

40G-1K Sess. TCP + UDP Offload Engine

- Highly customizable hardware IP block. Easily portable to ASIC flow, Xilinx/Altera FPGAs or Structured/ASIC flow.

- Eighth Generation TOE and System Solutions provide ‘Ultra-Low Latency’ and Ultra-High Performance with highest TCP bandwidth in Full Duplex. Network Tested and mature TCP protocol offload implementation

- All stages of Full TCP stack implemented in High performance hardware

-

25G-1K Sess. TCP + UDP Offload Engine

- Highly customizable hardware IP block. Easily portable to ASIC flow, Xilinx/Altera

- FPGAs or Structured/ASIC flow.

- Eighth Generation TOE and System Solutions provide ‘Ultra-Low Latency’ and Ultra-High Performance with highest TCP bandwidth in Full Duplex. Network Tested and mature TCP protocol offload implementation

- All stages of Full TCP stack implemented in High performance hardware