SPI flash memory controller IP

Filter

Compare

42

IP

from

20

vendors

(1

-

10)

-

-

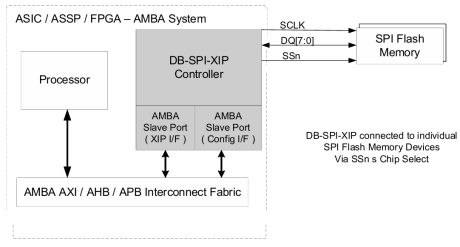

SPI XIP Flash Memory Controller IP – Programmable IO & Execute-In-Place (XIP) via second AMBA Interface

- The DB-SPI-XIP-FLASH-AMBA is a Serial Peripheral Interface (SPI) Controller Verilog IP Core supporting access to Single/Dual/Quad/Octal SPI Flash Memory devices by way of Processor Execute-in-Place (XIP).

- The DB-SPI-XIP-FLASH-AMBA is a SPI Master Controller targeting SPI NOR/NAND Flash Memories. The DB-SPI-XIP-FLASH-AMBA contains two AMBA Slave Interfaces: the first for Processor configuration or Processor access to the Flash Memory; the second for Processor AMBA Interface for Execute-in-Place (XIP) access to Flash Memory.

-

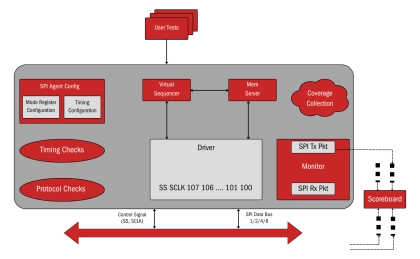

SPI Flash Controller - Ensures reliable validation of SPI Flash memory controllers

- The SPI Flash Controller Verification IP (VIP) is a powerful tool for verifying and simulating SPI Flash memory controllers in SoCs. It supports single, dual, and quad SPI modes, enabling seamless validation of read, write, erase, and advanced operations.

- This VIP is designed for diverse applications, including IoT devices, automotive systems, consumer electronics, and aerospace. It ensures efficient performance, low power usage, and reliable integration of SPI Flash memory in mission-critical and everyday devices

-

SPI FLASH Controller with Execute in place – XIP (SINGLE, DUAL and QUAD SPI Bus Controller with DDR / DTR support and optional AES Encryption)

- Set of software accessible control registers to execute any Flash memory command

- Supports any device clock frequency, polarity and phase,

- Programmable baud rate generator,

- Built in FLASH Commands decoder supports most popular FLASH devices,

-

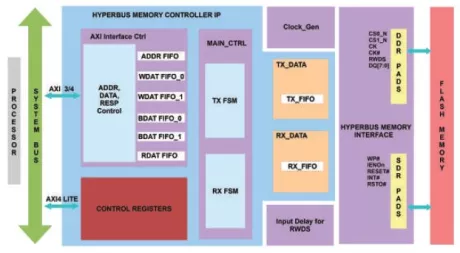

Hyperbus Flash Memory Controller

- Compatible with spansion hyperbus based memory products.

- 0 Wait State Write Burst Operation for HyperBus memory on AXI interface of up to 256 words.

-

QSPI FLASH Controller – XIP functionality (SINGLE, DUAL and QUAD SPI Bus Controller with Double Data Rate support)

- Set of software accessible control registers to execute any Flash memory command

- Supports any device clock frequency, polarity and phase,

- Programmable baud rate generator,

- Built in FLASH Commands decoder supports most popular FLASH devices,

-

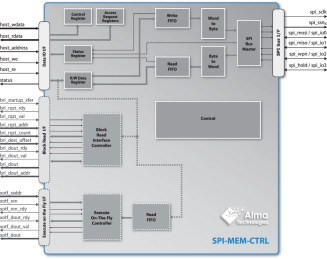

Host controller IP for controlling flash and other devices on the SPI bus: Quad SPI, Octal SPI, and xSPI

- Flexibility: Multiple SPI protocol support within single IP

- Simplicity: PHY-less IoT operation, or soft storage combo PHY IP simplifies SoC timing

- High Performance: Supports maximum Quad SPI / Octal SPI data rates and XIP (Execute In Place)

-

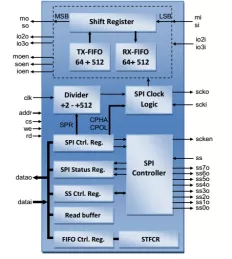

Quad SPI Controller

- The SPI controller support master/slave operation over the single-lane, dual-lane,quad-lane and half duplex singlelane protocols

- Programmable clock polarity and phase (CPOL/CPHA)

- Configurable MSB First or LSB First

- Master/Slave mode configurable frequency (FPCLK/2 max)

- SPI bus busy status flag

-

PSRAM Memory Controller IP

- DFSPI – SPI FLASH Controller with Execute in place – XIP (SINGLE, DUAL and QUAD SPI Bus Controller with DDR / DTR support and optional AES Encryption) + … NOR & NAND Flash Memory Support

-

HYPERBUS™ Memory Controller

- The HyperBus™ Memory Controller IP Core is a high-speed, fully configurable SPI master/slave solution, designed for seamless integration into modern SoC and FPGA architectures.

- Building on the proven DFSPI core, this IP bridges easily to APB, AHB, and AXI buses, supporting SINGLE, DUAL, QUAD, and OCTAL SPI modes for maximum design flexibility.