SATA IP

Filter

Compare

342

IP

from

43

vendors

(1

-

10)

-

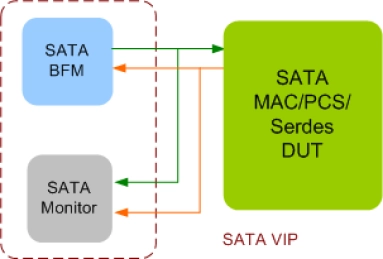

Verification IP for SATA

- Avery SATA VIP support verification of host and device and expansion targets.

- A variety of standards-based conformance test suites are also supported to ensure complete verification closure of your design to specification compliance

-

SATA Verification IP

- Supports SATA specs 2.5/2.6/3.0/3.1/3.2/3.3/3.4/3.5.

- Supports 1.5, 3 and 6 Gbps speeds.

- Supports Port Multiplier Discovery and Enumeration.

- Supports following interfaces

-

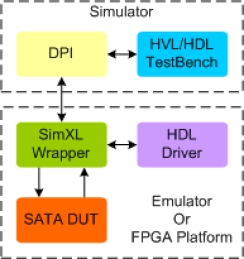

SATA Synthesizable Transactor

- Supports SATA specs 2.5/2.6/3.0/3.1/3.2/3.3/3.4/3.5.

- Supports 1.5, 3 and 6 Gbps speeds.

- Supports Port Multiplier Discovery and Enumeration.

- Supports TBI interface with following bits

-

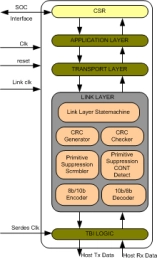

SATA HOST CONTROLLER IIP

- Supports SATA specs 2.5/2.6/3.0/3.1/3.2/3.3/3.4/3.5.

- Fully synthesizable

- Static synchronous design

- Positive edge clocking and no internal tri-states

-

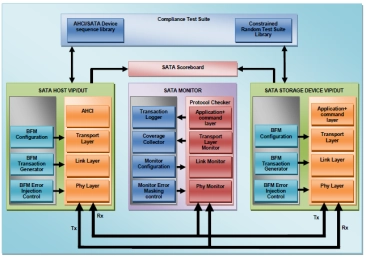

SATA 3.3 Verification IP

- Compliant to SATA 3.3, PIPE and AHCI 1.3.1 Specification and backward Compatible to SATA 1.0 ,SATA 2.0 and SATA 3.2 specification.

- Supports AHCI functionality on Host (HBA) side.

- Supports complete functionality of Application, Command, Transport, Link and PHY Layer.

- Configurable PIPE Interface width 8,16 or 32 bits.

-

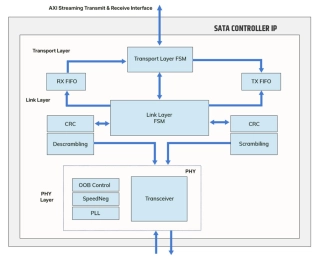

SATA 3 Controller IP

- Simple AXI streaming TX and RX interface for application layer communication.

- It supports Native Command Queuing and key primitives/FIS types from SATA specifications.

- Compliant with Serial ATA 3.0 specification.

- Supports data rates of 1.5/3/6 Gbit/s.

-

SATA 6G PHY in GF (40nm, 28nm)

- Compliant with SATA/eSATA v3.3, AHCI v1.3 and SATA PIPE v4.3 specifications

- AMBA 2.0 AHB and AMBA 3 AXI subsystem interfaces

- AMBA 4 AXI and ACE-Lite bus interfaces

- Memory data protection and memory address parity protection

-

SATA 6G PHY

- ? 6-Gbps transmission rate through standard SATA cable

- ? Spread-spectrum clock (SSC) generation and absorption

- ? Programmable down-spread (+4,980 ppm through -4,980 ppm)

- ? Fully clock-forwarded transceiver interface, configurable using soft PMA layer above hard macro PHY

-

USB 3.0/ PCIe 2.0/ SATA 3.0 Combo PHY IP, Silicon Proven in SMIC 14SF+

- Compatible with PCIe/USB3/SATA base Specification

- Fully compatible with PIPE3.1 interface specification

- Data rate configurable to 1.5G/2.5G/3G/5G/6G for different application

- Support 16-bit or 32-bit parallel interface when encode/decode enabled

-

USB 3.0/ PCIe 2.0/ SATA 3.0 Combo PHY IP, Silicon Proven in UMC 55SP/EF

- Compatible with PCIe/USB3/SATA base Specification

- Fully compatible with PIPE3.1 interface specification

- Data rate configurable to 1.5G/2.5G/3G/5G/6G for different application

- Support 16-bit or 32-bit parallel interface when encode/decode enabled