Power Management Network IP

Filter

Compare

242

IP

from

33

vendors

(1

-

10)

-

Software tool for the automatic building of Power Management Unit (PMU)

- PowerStudio is an innovative software d to speed up the architecture, design and integration of complex, automotive-grade on-chip Power Management Units (PMU).

- It combines in a single tool a versatile solution for power network exploration with a unique capability to generate pre-verified RTL and UPF files of the power network.

-

Power efficient, high-performance neural network hardware IP for automotive embedded solutions

- Power efficient, high-performance

- For automotive embedded solutions

-

Data Movement Engine - Turnkey network compute subsystem for data movement applications.

- Industrial Networking: Rapid packet processing of data through multiple, switched ethernet ports with support for factory automation protocols

- 5G/6G Communications: Scalable L2/L3 Ethernet switch with flexible port counts/speeds, including TSN and security

- Automotive Gateway: High-speed data packet networking with multiple communication interfaces and support for switching and bridging

- Datacenter Infrastructure: Standalone data processing units to handle highly multiplexed data streams corresponding to millions of network connections with high efficiency and low power

-

Run-time Reconfigurable Neural Network IP

- Customizable IP Implementation: Achieve desired performance (TOPS), size, and power for target implementation and process technology

- Optimized for Generative AI: Supports popular Generative AI models including LLMs and LVMs

- Efficient AI Compute: Achieves very high AI compute utilization, resulting in exceptional energy efficiency

- Real-Time Data Streaming: Optimized for low-latency operations with batch=1

-

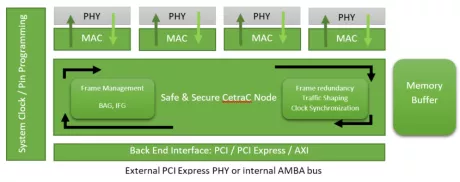

Multi Protocol Endpoint IP Core for Safe and Secure Ethernet Network

- "Ethernet/TSN/ARINC664P7 EndSystem with customizable number of ports up to 1 Gbps.

- Support IEEE 1588 PTPV2 as GrandMaster or User

- Safe & Secure Ethernet communication

- Multi-protocol

-

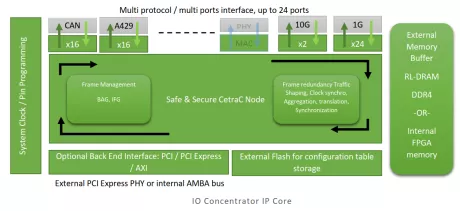

Multi Protocol IO Concentrator (RDC) IP Core for Safe and Secure Ethernet Network

- Ethernet/ARINC664P7 Switch with customizable number of ports up to 1 Gbps.

- Support IEEE 1588 PTPV2 as GrandMaster or User

- Safe & Secure Ethernet communication

- Multi-protocol : CAN, ARINC429, MIL-STD-1553, TSN

-

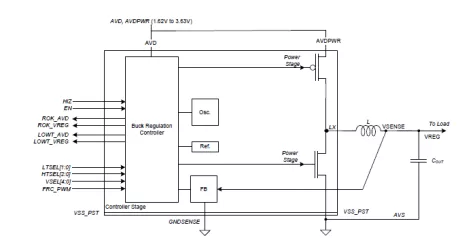

DC/DC Buck Regulator

- High efficiency buck regulator (up to 95% in peak), thanks to dual mode (dm) controller

- Pulse Frequency Modulation (PFM) mode at low load and Pulse With Modulation (PWM) mode at high load.

- Low Bill-Of-Material: fully integrated feedback and active compensation loop do not require additional external passive components.

- Behavioral models: ease integration in SoC and optimized Power Management Network (PMNet) by verifying mode transitions as well as noise propagation

-

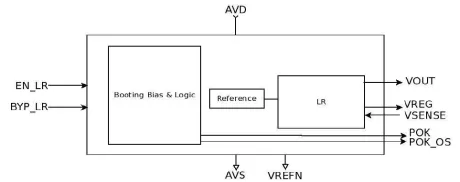

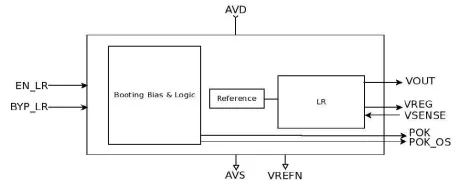

Linear regulator, low-noise optimized for sensitive analog loads such as CODEC and Reference

- Starring a PSRR of -65 dB at 20 kHz and a low intrinsic noise, combined with a low quiescent current of 110 uA, the nLR-VAIPO helps optimize the power management network for audio handheld applications such as smartphone and tablet.

- Small footprint: only 0.12 mm2 (including bandgap reference and POK circuit)

- Minimization of the overall system power, through the support of 3 modes of operation: normal, shutdown and bypass

- Eases integration in SoC nLR-VAIPO is delivered with behavioral models. These new views enable to build an optimized Power Management Network (PMNet) by verifying mode transitions as well as noise propagation.

-

Linear regulator, low-noise optimized for sensitive analog loads such as CODEC and Reference

- Starring a PSRR of -65 dB at 20 kHz and a low intrinsic noise, combined with a low quiescent current of 110 uA, the nLR-VAIPO helps optimize the power management network for audio handheld applications such as smartphone and tablet.

- Small footprint: only 0.12 mm2 (including bandgap reference and POK circuit)

- Minimization of the overall system power, through the support of 3 modes of operation: normal, shutdown and bypass

- Eases integration in SoC nLR-VAIPO is delivered with behavioral models. These new views enable to build an optimized Power Management Network (PMNet) by verifying mode transitions as well as noise propagation.

-

DC/DC Buck Regulator

- High efficiency buck regulator (up to 95% in peak), thanks to dual mode (dm) controller

- Pulse Frequency Modulation (PFM) mode at low load and Pulse With Modulation (PWM) mode at high load.

- Low Bill-Of-Material: fully integrated feedback and active compensation loop do not require additional external passive components.

- Behavioral models: ease integration in SoC and optimized Power Management Network (PMNet) by verifying mode transitions as well as noise propagation