ONFI memory controller IP

Filter

Compare

16

IP

from

10

vendors

(1

-

10)

-

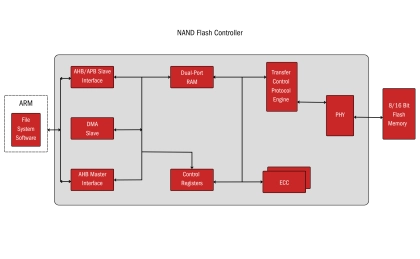

NAND Memory Controller

- The NAND memory controller IP core is compliant with the ONFI standard working on asynchronous mode.

- This core also supports error correction on the fly without any processor intervention. Up to 8 memory chips can be accessed on the same bus with write speed of 100Mbps and read speeds of 120Mbps.

-

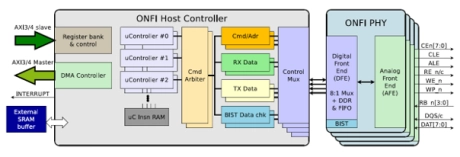

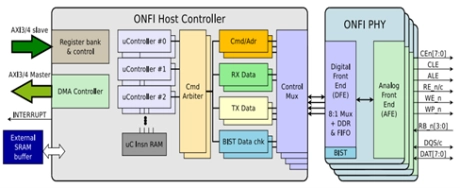

ONFI PHY & Controller

- The ONFI IP provides Turnkey solutions for IC requiring access to ONFI-compatible NAND Flash devices

- Optimized for low power and high-speed applications, it features robust timing and a compact silicon area

- It supports all ONFI NAND Flash components available on the market

-

ONFI 3.2 NAND Flash Controller IP Compliant to JEDEC

- Compliant to ONFI 3.2 Specification

- Supports SDR, NV-DDR and NV-DDR2

- Included synthesizable PLL/DLL

- ONFI 3.2 compatible 1.8v NV-DDR2 I/O pads supporting up to 533MT/s is available

-

ONFI 2 NAND Flash Controller IP Compliant to JEDEC

- The ONFI 2.3 NAND Flash Controller IP Core is a full-featured, easy to use, synthesizable core, easily integrated into any SoC or FPGA development.

- Designed to support both SLC and MLC flash memories, ONFI 2.3 NAND controller IP is flexible in use and easy in implementation.

-

ONFI 4.2 NAND Flash Controller & PHY IP Compliant to JEDEC

- The NAND Flash Controller IP Core is a full-featured, easy to use, synthesizable core, easily integrated into any SoC or FPGA development.

- Designed to support SLC, MLC and TLC flash memories, it is flexible in use and easy in implementation. The controller works with any suitable NAND Flash memory device up to 1024Gb from leading memory providers – Micron, Samsung, Toshiba and Hynix.

-

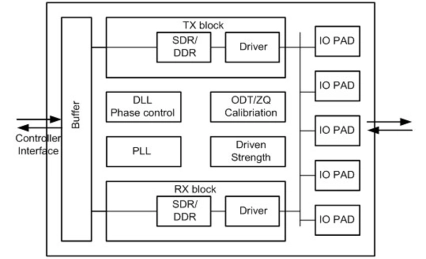

ONFI 3.2 NAND Flash PHY IP Compliant to JEDEC

- Compliant to ONFI revision 3.2 standard

- Silicon proven PLL to support all frequencies from 10MHz to 266MHz, and DLL to improve data sampling accuracy dynamically

- Include ONFI 3.2 I/O pads compatible to 1.8v NV-DDR2 533 MT/s and 3v NV-DDR 200 MT/s

- Supports NV-DDR2 mode of operation supporting up to 266MHz

-

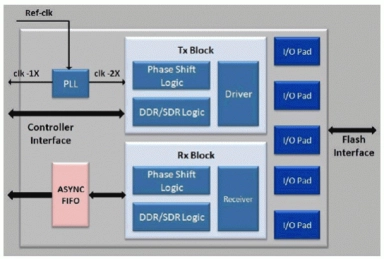

ONFI 5.0 NAND Fash PHY IP Compliant to JEDEC

- The ONFI 5.0 PHY IP is designed to connect seamlessly with their ONFI 5.0 Host Controller IP.

- The ONFI 5.0 PHY has complete SDR, NV-DDR, NV-DDR2, NV-DDR3 and NV-LPDDR4 TX/RX functionality and supports all the speeds defined in the ONFI specification while remaining backwards compatible with the prior versions of the ONFI specifications.

-

ONFI 4.2 NAND Flash Software Driver

- The NAND Flash Controller IP Core is a full-featured, easy to use, synthesizable core, easily integrated into any SoC or FPGA development. Designed to support SLC, MLC and TLC flash memories, it is flexible in use and easy in implementation.

- The controller works with any suitable NAND Flash memory device up to 1024Gb from leading memory providers – Micron, Samsung, Toshiba and Hynix.

-

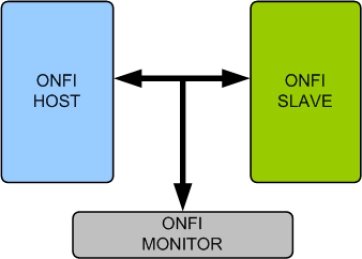

NAND Flash Controller - Ensures robust NAND Flash interface validation for reliable designs

- The NAND Flash Controller Verification IP (VIP) is a specialized tool for validating and simulating NAND Flash memory interfaces in System-on-Chip (SoC) designs. It ensures compliance with protocols, error correction, and optimal performance across varied conditions.

- This versatile tool supports a wide range of applications, including automotive, consumer electronics, industrial automation, and aerospace. By guaranteeing reliable integration of NAND Flash memory, it enables seamless functionality in devices ranging from gaming consoles to mission-critical systems

-

Open Nand Flash Interface (ONFI)

- Compliant with ONFI 2.3/3.0/4.0/4.1/5.0 specifications.

- Supports Source Synchronous and Asynchronous data interfaces.

- Supports all mandatory and optional commands.

- Supports 16 bit bus width operations.