Mobile PCI Express IP

Filter

Compare

28

IP

from

7

vendors

(1

-

10)

-

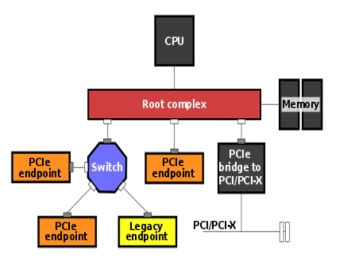

PCIe - PCI Express Controller

- The PCIe 3.0 (Peripheral Component Interconnect Express 3.0) is a computer hardware interface standard that is used to connect various components to a computer's motherboard.

- It is the third generation of the PCIe standard and offers increased bandwidth, improved performance, and reduced power consumption compared to its predecessor, PCIe 2.0 Overall, PCIe 3.0 provides faster and more efficient communication between the various components in a computer, including graphics cards, network adapters, and storage devices, resulting in better overall performance.

-

7 Series Integrated Block for PCI Express (PCIe)

- Compliant with the PCI Express Base Specification 2.1

- Fully compliant with PCI Express transaction ordering rules

- Supports maximum payload of 1024 bytes (for most configurations)

- 1 Virtual Channel

-

7 Series Gen2 Integrated Block for PCI Express (PCIe)

- Compliant with the PCI Express Base Specification 2.1

- Fully compliant with PCI Express transaction ordering rules

- Supports maximum payload of 1024 bytes (for most configurations)

- 1 Virtual Channel

-

Virtex-6 Integrated Block for PCI Express (PCIe)

- High Performance and High Bandwidth applications

- Compute and Data Co-processing Applications

- Medical Imaging, High-Performance Computing & Communications Packet Processing

-

Spartan-6 FPGA Integrated Endpoint Block for PCI Express (PCIe)

- Compliant with the PCI Express Base Specification 1.1

- Fully compliant with PCI Express transaction ordering rules

- Supports maximum payload of 512 bytes

- 1 Virtual Channel

-

Endpoint for Gen1 PCI Express

- Protocol and electrically compatible

- Complete endpoint solution includes physical, link and transaction, and configuration management modules

- Both 8-lane and 4-lane configurations auto negotiate down to a 1-lane configuration

- Supports packet-oriented LocalLink Interface

-

Virtex-5 Endpoint Block Plus Wrapper for PCI Express (PCIe)

- Compliant with the PCI Express Base Specification 1.1

- Fully compliant with PCI Express transaction ordering rules

- Supports maximum payload of 512 bytes

- 1 Virtual Channel

-

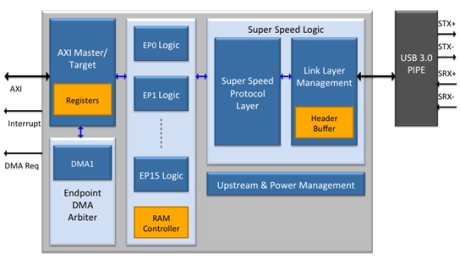

USB 3.0 Device Upgrade IP Core

- The USB 3.0 Device Upgrade provides a dedicated dual simplex, routable packet architecture for USB3.0 packet transfers, with a disable option for power savings.

- The USB 3.0 Upgrade IP supports all power management features as well as a dedicated link manager for each downstream port for increased efficiency.

-

USB 3.0 Device

- USB 3.0 Compliance

- SuperSpeed: 5 Gbit/s

- Hish Speed: 480Mbit/s

- Full Speed: 12Mbit/s

- 8/16/32 bit USB 3.0 PIPE interface

-

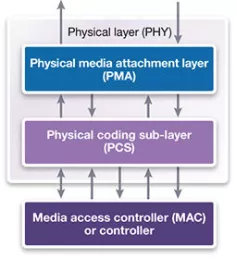

Multiprotocol 10G PHY, TSMC N7 x2, North/South (vertical) poly orientation

- Supports 1.25 Gbps to 10 Gbps data rates

- Supports PCI Express 3.1, SATA 6G, SGMII

- Supports x1 to x16 macro configurations