Mobile DDR Memory Controller IP

Filter

Compare

57

IP

from

7

vendors

(1

-

10)

-

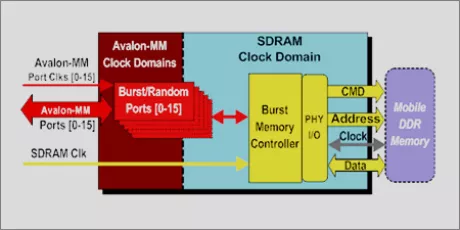

Avalon Mobile DDR Memory Controller

- 200 MHz Cyclone / Stratix memory performance

- Supports all standard Mobile DDR SDRAM devices

- 1 to 16 Avalon® independent local bus port interfaces

- Avalon Pipelined and Burst transfers

-

DO-254 DDR Memory Controller 1.00a

- DDR, DDR2, DDR3, and LPDDR (Mobile DDR) memory standards support

- Up to 800 Mb/s (400 MHz double data rate) performance

- Up to four MCB cores in a single Spartan-6 device

- Configurable dedicated multi-port user interface to FPGA logic

-

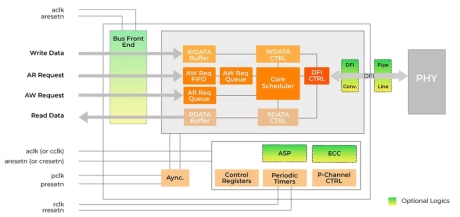

Performance Enhanced version of DDR Enhanced Memory Ctl (uMCTL2) supporting DDR4, DDR3, DDR2, LPDDR4, LPDDR3, and LPDDR2

- Select a complete multi-ported Enhanced Universal DDR Memory Controller offering 1 to 16 host ports, or join a third-party scheduler to a single-port Enhanced Universal Protocol Controller

- Support for JEDEC standard DDR2, DDR3, DDR4, LPDDR/Mobile DDR, LPDDR2, LPDDR3, and LPDDR4 SDRAMs

- Compatible with all Synopsys DDR PHYs (excluding DDR2/DDR PHYs) using DFI-compliant interfaces

-

-

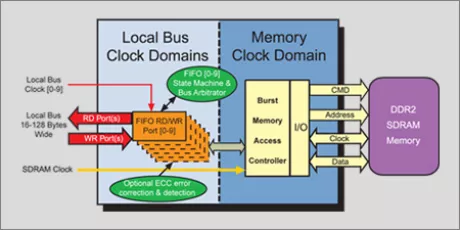

Streaming Multi-port SDRAM Memory Controller

- 200/333 MHz (400/666 Mbps) Cyclone / Stratix memory performance

- SDR, DDR, DDR2, and Mobile DDR SDRAM memory devices

- Up to 10 native RD or WR ports

- Memory data width: 8/16/32/64-bit

-

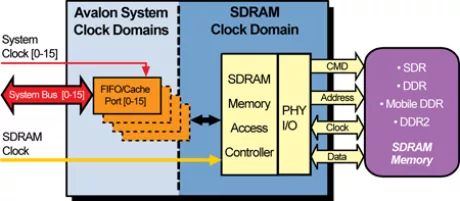

Avalon Multi-port SDRAM Memory Controller IP Core

- 200 / 333 MHz (400/666 Mbps) Cyclone / Stratix DDR2 memory performance

- SDR, DDR, DDR2 and Mobile DDR SDRAM Memory Devices

- From 1 to 16 Avalon-MM local bus port interfaces

- Memory bandwidth utilization in excess of 95%

-

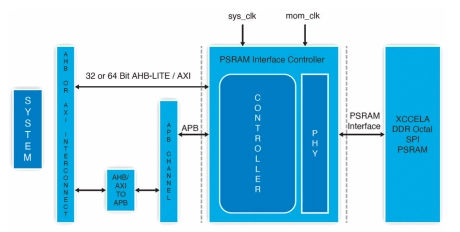

Octal SPI DDR PSRAM controller

- This controller supports AP Memory’s Xccela open standard Bus for digital interconnect and data communications, suitable for non-volatile and volatile memories such as PSRAM.

- This controller enables smooth integration AP memory’s of Xccela PSRAM memory chips into various new-gen devices made with mobile and wearable low power SoCs’.

- This memory controller implementation is designed to give the user full flexibility for driving the memory control signals and timing adjustment for data sampling.

-

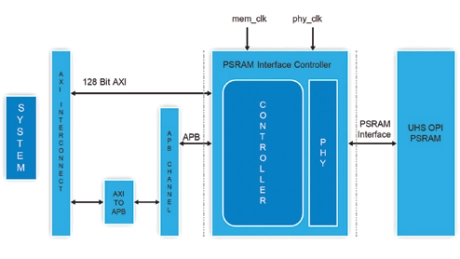

AP Memory UHS PSRAM Controller

- This controller supports AP Memory’s UHS series of high speed PSRAM devices which can clock frequencies of upto 1066 MHz.

- This controller enables smooth integration of APMemory’s UHS OPI PSRAM memory device chips into various new-gen devices made with mobile and wearable low power SoCs’.

- This memory controller implementation is designed to give the user full flexibility for driving the memory control signals and timing adjustment for data sampling.

-

DDR Enhanced Protocol Controller (uPCTL2) supporting DDR4, DDR3, DDR2, LPDDR4, LPDDR3, and LPDDR2

- Select a complete multi-ported Enhanced Universal DDR Memory Controller offering 1 to 16 host ports, or join a third-party scheduler to a single-port Enhanced Universal Protocol Controller

- Support for JEDEC standard DDR2, DDR3, DDR4, LPDDR/Mobile DDR, LPDDR2, LPDDR3, and LPDDR4 SDRAMs

- Compatible with all Synopsys DDR PHYs (excluding DDR2/DDR PHYs) using DFI-compliant interfaces

-

LPDDR6/5X/5 Controller IP

- Supports JEDEC standard LPDDR6, LPDDR5X and LPDDR5 SDRAMs

- Support for data rates up to 14.4 Gbps for LPDDR6, 10.67 Gbps for LPDDR5X, and 6.4 Gbps for LPDDR5

- Multiport Arm® AMBA® interface AXI™4 with managed QoS or single-port host interface to the DDR controller

- DFI 5.2 compliant interface to Synopsys LPDDR6/5X/5 PHY