MSC IP

Filter

Compare

15

IP

from

9

vendors

(1

-

10)

-

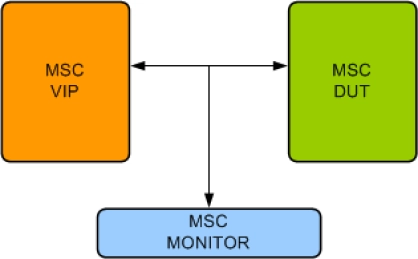

Microsecond Channel (MSC) Verification IP

- Compliant to 2005-01-0057 specification.

- Supports high speed synchronous downstream and low speed asynchronous upstream

- bus.

- Supports bidirectional interface.

-

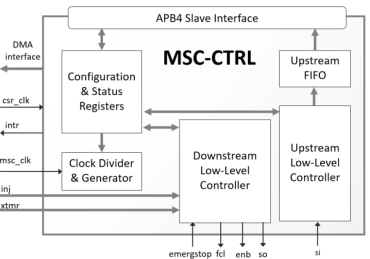

Microsecond Channel (MSC/MSC-Plus) Controller

- The MSC-CTRL IP core implements a high-speed serial interface controller designed to connect a microcontroller or SoC to external power devices or sensors.

- It implements the Microsecond Channel (MSC) and Microsecond Channel Plus (MSC-Plus) protocols—derived from the Microsecond Bus (uSB) serial concept—and acts as a bus master for downstream transmission and as a bus slave for upstream transmission.

-

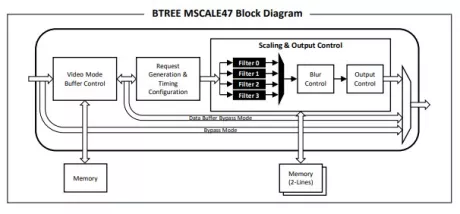

Scaler IP - MSCALE

- Silicon Proven Several Times for Mobile Phone

- Use Small Gate Counts

- Optimized for Power Saving

-

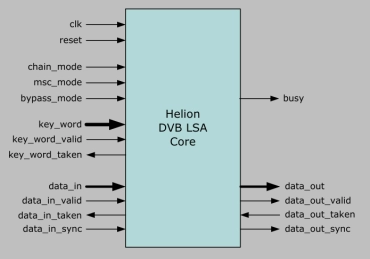

DVB Local Scrambling Algorithm Core

- The Helion DVB LSA Scrambler and Descrambler cores implement the Local Scrambling Algorithm as specified to provide MPEG-2 Transport Stream packet security within DVB Content Protection and Copy Management (DVB-CPCM) compliant systems.

- Both cores provide all operations required to scramble or descramble MPEG-2 TS packets, including IV generation using either MSC Data Independent (MDI) or MSC Data Dependent (MDD) mode, and payload protection using either AES-CBC or AES-RCBC cipher chaining modes.

-

IEEE 802.15.3c Irregular LDPC(672,336), LDPC(672,504), LDPC(672,588) encoder and decoder

- Belief-propagation iterative decoding

- Pipeline design, 4 clocks perdecoding iteration

- Single clock synchronous design; registered inputs and outputs;

- Single-port memories only

-

DAB modulator

- Fully compliant with ETSI EN 300 401 V1.4.1 2006-06, for DAB

- DAB-Modes: I, II, III, IV

- All protection levels supported

- Synchronous design

-

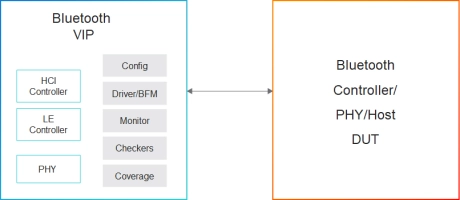

Simulation VIP for Bluetooth

- Advertiser

- High Duty, Low Duty, Directed, Undirected, Connectable, Non-connectable Advertisement

- Scanner/Initiator

- Active/Passive Scanning

-

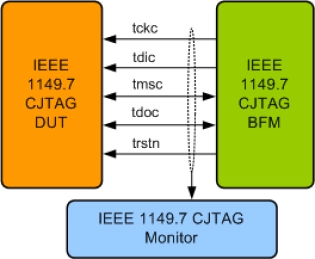

CJTAG (IEEE 1149.7) Verification IP

- Fully compatible with IEEE 1149.7 standard.

- Can be used as TAP controller (slave) or TAP instruction/data generator (Master) for CJTAG.

- Comes with CJTAG monitor to check and report any protocol violation.

- Supports TAP.7 capability classes T0 to T5

-

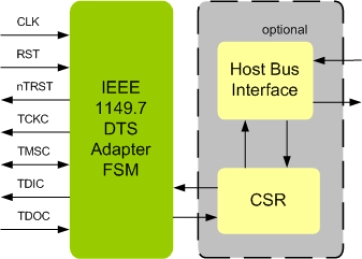

IEEE 1149.7 DTS ADAPTER IIP

- Compliant with IEEE 1149.7 standard specification.

- Full IEEE 1149.7 DTS Adapter functionality.

- Supports IEEE 1149.7 classes T0 to T5.

- Supports Reset and Escape sequences generation of TAP controller.

-

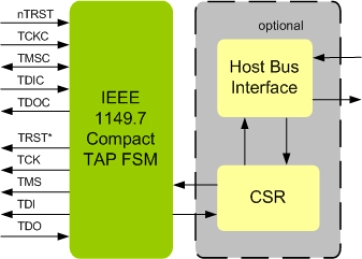

IEEE 1149.7 COMPACT TAP IIP

- Compliant with IEEE 1149.7 standard specification.

- Supports TAP.7 capability classes T0 to T5.

- Supports Reset and Selection Unit (RSU) for class T0 optional features.

- Supports Extended Protocol Unit (EPU) for classes T0 to T3.