MIPI I3C PHY I/O IP

Filter

Compare

15

IP

from

4

vendors

(1

-

10)

-

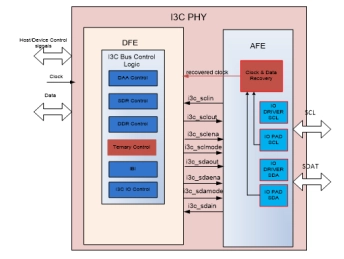

I3C PHY

- The I3C bus is used for various sensors in the mobile/automotive system where the Host transfers data and control between itself and various sensor devices.

- The I3C interface is intended to improve upon the features of the I2C interface, preserving backward compatibility.

-

I3C PHY & Controller

- DTI I3C Controller provides the logic consistent with NXP I3C specification to support the communication of low-speed integrated circuits through I3C bus.

- The IP facilitates software controllable by application processor through industry-standard AMBA interface. The bus interface is flexible and easily integrated into APB, AHB or AXI system bus.

-

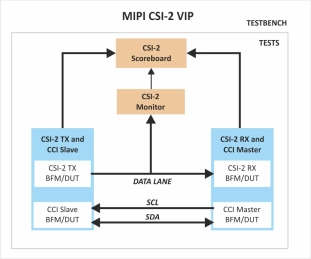

MIPI CSI-2 with C-PHY Verification IP

- Compliant to MIPI CSI-2 Specification Version 4.0.1 along with MIPI C-PHY Specification Version 2.1 with PPI interface

- Supports upto 32 virtual channels with C-PHY

- C-PHY supports MFEN and SFEN for CSI-2 TX and RX respectively for Data Lane greater than 1

- C-PHY supports MFAA and SFAA for CSI-2 TX and RX respectively for Data Lane 1 module

-

MIPI CSI-2 V4 Host Controller Stnd

- Supports key features of the latest MIPI CSI-2 specification

- PPI interface to MIPI C-PHY v1.2 and D-PHY v2.1

- Programmable multi-lane merging

- Short and long packet format and all primary and secondary CSI-2 data formats

-

MIPI CSI-2 V4 Host Controller Prem

- Supports key features of the latest MIPI CSI-2 specification

- PPI interface to MIPI C-PHY v1.2 and D-PHY v2.1

- Programmable multi-lane merging

- Short and long packet format and all primary and secondary CSI-2 data formats

-

MIPI CSI-2 V4 Host Controller Plus

- Supports key features of the latest MIPI CSI-2 specification

- PPI interface to MIPI C-PHY v1.2 and D-PHY v2.1

- Programmable multi-lane merging

- Short and long packet format and all primary and secondary CSI-2 data formats

-

MIPI CSI-2 V4 Host Controller ASIL Compliant

- Supports key features of the latest MIPI CSI-2 specification

- PPI interface to MIPI C-PHY v1.2 and D-PHY v2.1

- Programmable multi-lane merging

- Short and long packet format and all primary and secondary CSI-2 data formats

-

MIPI CSI-2 V4 Device Controller Stnd

- Supports key features of the latest MIPI CSI-2 specification

- PPI interface to MIPI C-PHY v1.2 and D-PHY v2.1

- Programmable multi-lane merging

- Short and long packet format and all primary and secondary CSI-2 data formats

-

MIPI CSI-2 V4 Device Controller Prem

- Supports key features of the latest MIPI CSI-2 specification

- PPI interface to MIPI C-PHY v1.2 and D-PHY v2.1

- Programmable multi-lane merging

- Short and long packet format and all primary and secondary CSI-2 data formats

-

MIPI CSI-2 V4 Device Controller Plus

- Supports key features of the latest MIPI CSI-2 specification

- PPI interface to MIPI C-PHY v1.2 and D-PHY v2.1

- Programmable multi-lane merging

- Short and long packet format and all primary and secondary CSI-2 data formats