MIPI DSI Host Controller IP

Filter

Compare

22

IP

from

6

vendors

(1

-

10)

-

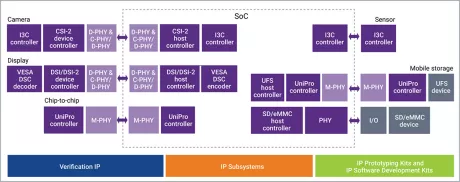

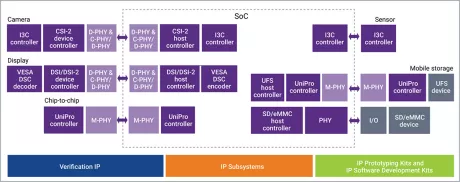

MIPI DSI Host Controller

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

MIPI DSI Host Combo Controller

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

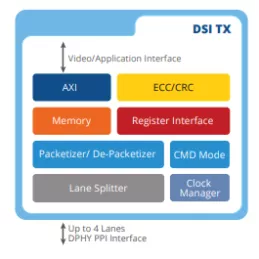

MIPI DSI TX Controller Subsystem

- Compliant with the MIPI DSI Interface Specification, rev. 1.3

- Standard PPI interface towards D-PHY

- 1-4 Lane Support

- Maximum Data Rate – 1.5 Gigabits per second

-

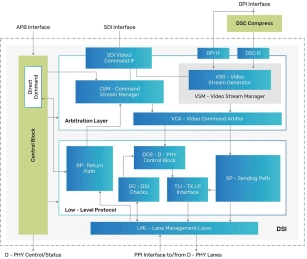

MIPI DSI TX Controller

- Compliant with MIPI DSI v1.3.1

- Supports both Command Mode and Video Mode

- Supports bi-directional low-power data transmission (LPDT)

- Cadence Serial Display Interface (SDI), MIPI Display Pixel Interface (DPISM), and Display Compression (DSC) input interface options

-

MIPI DSI-2 V2 Host Controller Prem

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

MIPI DSI-2 V2 Host Controller ASIL Compliant

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

DSI Receiver Controller

- The DSI v1.3 Receiver Controller IP is designed to provide MIPI DSI 1.3 compliant high-speed serial connectivity for device (mobile display modules) with Type 1 to 4 architectures.

- Serial connectivity to the mobile applications processor’s DSI host is implemented using 1 to 4 D-PHY’s (also available from Arasan), depending on display bandwidth needs.

-

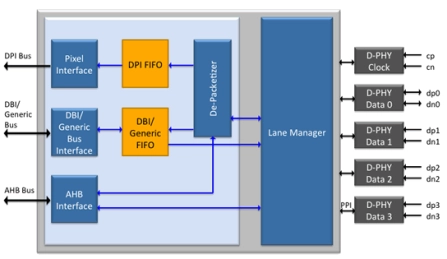

MIPI DSI-2 Transmitter Controller IP Core

- The MIPI Display Serial Interface (DSI-2) Transmitter (host processor interface) Controller IP provides a high-speed serial interface between an application processor and display modules using either MIPI C-PHY v1.1 or MIPI D-PHY v1.2 and v2.0.

-

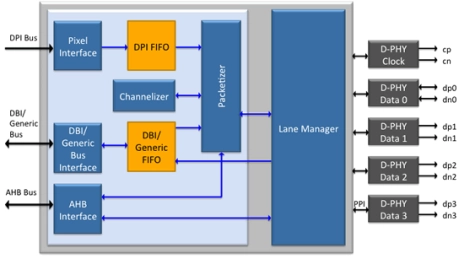

MIPI DSI-2 Transmitter v1.1 Controller IP, Compatible with MIPI D-PHY & C-PHY

- Compliant with MIPI DSI-2 Standard v0.8.x, MIPI D-PHY Standard v1.x, MIPI D-PHY Standard V2.x and MIPI C-PHY V1.x

- Up to 3 Gsps per trio using C-PHY. 17Gbps in 3 Trios

- Up to 2.5 Gbps per data lane of D-PHY (V2.0). 10Gbps in 4 Lanes

- Programmable 1, 2, 3 (C-PHY) or 4 (D-PHY) Data Lane Configuration