MIPI CSI-2 v2.1 IP

Filter

Compare

95

IP

from

9

vendors

(1

-

10)

-

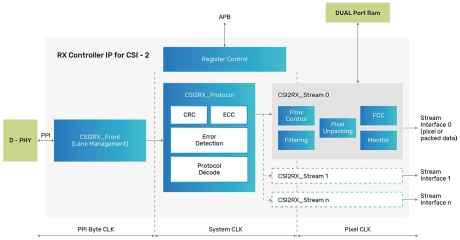

MIPI CSI-2 RX Controller

- Standards Compliant. CSI-2 v2.1, with 8-bit and 16-bit PPI data width and links with 1, 2, 4, or 8 data lanes

- Provides up to 8 Independent Stream Output Interfaces, allowing a highly configurable range of options, including multiple pixel modes, various buffering modes, packed data mode, Data Type selection, and Virtual Channel or Data Type interleaving

-

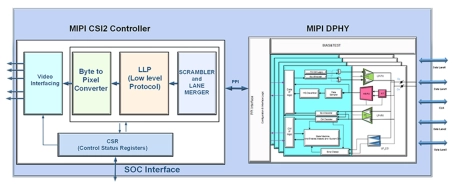

MIPI CSI2 Interface Solution

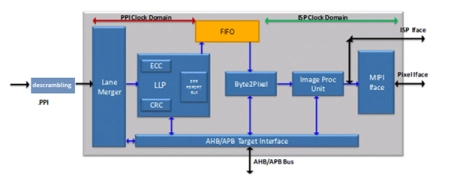

- Brite provides full solution for the MIPI CSI interface, which receives the data from sensors in PHY layer, and then converts the byte data to pixel after lane data mergence.

- Data scramble is an optional feature to decrease the EMI effect.

- A standard PPI interface is implemented for the connection between MIPI PHY and CSI controller. Brite MIPI CSI interface solution supports image applications with varying pixel formats.

-

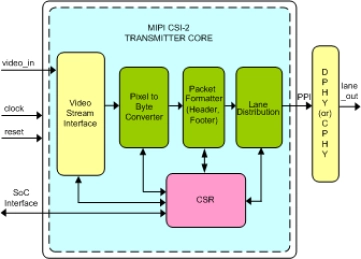

CSI-2 v2.1 Transmitter IP

-

Arasan IP Core that functions as a MIPI CSI-2 Transmitter, which typically resides in a mobile platform’s camera module, and communicates over a D-PHY/C-PHY link to a CSI2 Receiver in the applications processor.

-

The Arasan CSI-2 combo IP is MIPI-compliant and provides a standard, scalable, low-power, high-speed interface that supports a wide range of higher image resolutions.

-

-

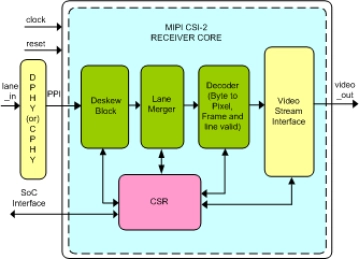

CSI-2 v2.1 Receiver IP

- Fully compliant to MIPI standard

- Small footprint

- Functionality ensured with comprehensive verification

- Product quality proven with silicon

-

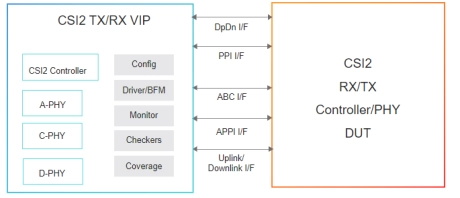

Simulation VIP for MIPI CSI-2

- Support testbench language interfaces for SystemVerilog, UVM, OVM, e, and SystemC

- Generates constrained-random bus traffic with predefined error injection at CSI-2, D-PHY, C-PHY and A-PHY levels

- Callbacks access at multiple TX and RX queue points for scoreboarding and data manipulation

-

MIPI CSI-2 Transmitter IIP

- Compliant with MIPI CSI-2 Specification v1.0, v1.1, v1.3, v2.0,v2.1

- Compliant with D - PHY Specification v1.1,v1.2,v2.0,v2.1

- Compliant with C - PHY Specification v0.7,v1.2,v2.0

- Full MIPI CSI-2 TRANSMITTER functionality where either D - PHY / C - PHY can be used

-

MIPI CSI-2 Receiver IIP

- Compliant with MIPI CSI-2 Specification v1.0, v1.1, v1.3, v2.0,v2.1

- Compliant with D - PHY Specification v1.1,v1.2,v2.0,v2.1

- Compliant with C - PHY Specification v0.7,v1.2,v2.0

- Full MIPI CSI-2 RX functionality where either D - PHY / C - PHY can be used

-

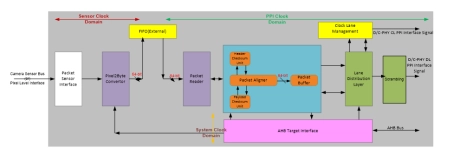

MIPI CSI-2 V4 Host Controller Stnd

- Supports key features of the latest MIPI CSI-2 specification

- PPI interface to MIPI C-PHY v1.2 and D-PHY v2.1

- Programmable multi-lane merging

- Short and long packet format and all primary and secondary CSI-2 data formats

-

MIPI CSI-2 V4 Host Controller Prem

- Supports key features of the latest MIPI CSI-2 specification

- PPI interface to MIPI C-PHY v1.2 and D-PHY v2.1

- Programmable multi-lane merging

- Short and long packet format and all primary and secondary CSI-2 data formats

-

MIPI CSI-2 V4 Host Controller Plus

- Supports key features of the latest MIPI CSI-2 specification

- PPI interface to MIPI C-PHY v1.2 and D-PHY v2.1

- Programmable multi-lane merging

- Short and long packet format and all primary and secondary CSI-2 data formats