Low-Latency 10/100/1000 Ethernet MAC IP

Filter

Compare

9

IP

from

3

vendors

(1

-

9)

-

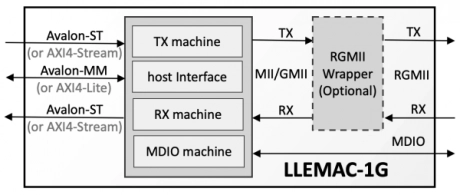

Low-Latency 10/100/1000 Ethernet MAC

- The LLEMAC-1G implements an Ethernet Media Access Controller (MAC) compatible with the 10/100 Mbps IEEE 802.3 and 1Gbps IEEE 802.3-2002 specifications.

- Featuring extremely low egress and ingress latency, the core is ideal for the implementation of TSN Ethernet nodes, live streaming and other devices requiring minimum latency in the reception and transition of Ethernet frames.

-

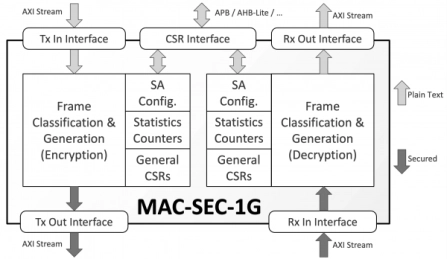

MACsec Protocol Engine for 10/100/1000 Ethernet

- The MAC-SEC-1G IP core implements a compact and configurable custom-hardware protocol engine for the IEEE 802.1AE (MACsec) standard.

- It supports all cipher suites provisioned by the MACsec standard and the VLAN-in-Clear improvement and is silicon- and performance-optimized for networks operating up to 1Gbps.

-

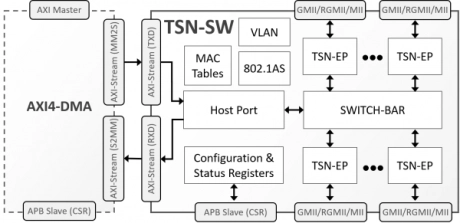

Multiport TSN Ethernet Switch

- The TSN-SW implements a highly flexible, low-latency, multiport TSN Ethernet switch.

- It supports the hardware functionality for Ethernet bridging according to the IEEE 802.1Q standard and implements the essential TSN timing synchronization and traffic-shaping protocols (i.e. IEEE 802.1AS-2020, 802.1Qav, 802.1Qbv, and 802.1Qbu, 802.1br).

-

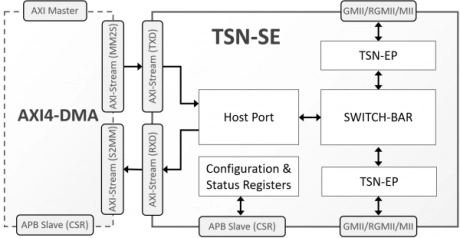

TSN Ethernet Switched Endpoint Controller

- The TSN-SE implements a configurable controller meant to ease the implementation of switched endpoints for Time Sensitive Net-working (TSN) Ethernet networks.

- It integrates hardware stacks for timing synchronization (IEEE 802.1AS-2020), traffic shaping (IEEE 802.1Qav and IEEE 802.1Qbv), frame-preemption (IEEE 802.1Qbu and IEEE 802.3br) and a low-latency Ethernet MAC.

-

-

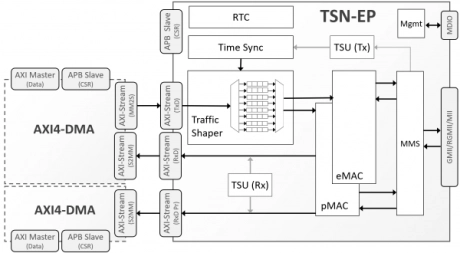

TSN Ethernet Endpoint Controller

- The TSN-EP implements a configurable controller meant to ease the implementation of endpoints for networks complying to the Time Sensitive Networking (TSN) standards.

- It integrates hardware stacks for timing synchronization (IEEE 802.1AS-2020) and traffic shaping (IEEE 802.1Qav and 802.1Qbv), frame-preemption (IEEE 802.1Qbu and IEEE 802.3br) and a low-latency Ethernet MAC.

-

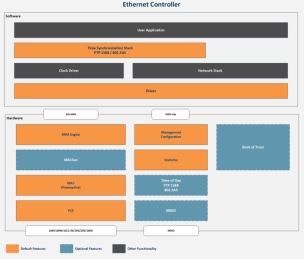

Ethernet Controller

- The Ethernet Controller is an ASIC proven high-performance, feature-rich network interface solution designed to deliver reliable, low-latency Ethernet connectivity across a broad range of embedded and enterprise applications.

- Comcores offers controllers ranging from 10M to 800G enabling seamless integration into systems requiring Ethernet connectivity.

-

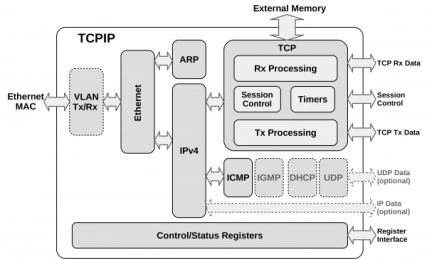

1G/10G TCP/IP Hardware Stack

- The TCPIP-1G/10G core implements a complete TCP/IP Hardware Protocol Stack.

- More capable than many offloading engines, it allows systems to connect to an Internet Protocol (IP) network and exchange data using the TCP protocol without requiring assistance from — or even the presence of — a system processor.

-

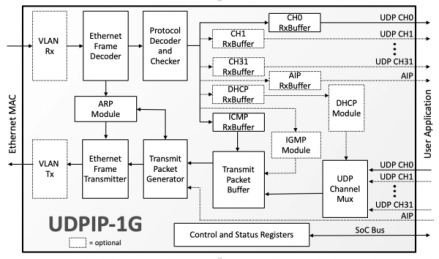

UDP/IP Hardware Protocol Stack

- Implements a UDP/IP hardware protocol stack that enables high-speed communication over a LAN or a point-to-point connection.

- Designed for standalone operation, the core is ideal for offloading the host processor from the demanding task of UDP/IP encapsulation and enables media streaming with speeds up to 1 or 10Gbps, depending on the speed of the silicon fabric, even in processor-less SoC designs.