Linear Regulator IP

Filter

Compare

225

IP

from

19

vendors

(1

-

10)

-

Retention Alternative Regulator, combines a linear regulator and an ultra-low quiescent regulator for sleep mode in TSMC 40uLPeF

- Support input supply voltage up to 3.63V

- Programmable output voltage from 0.5V to 3.3V

- Performances in sleep mode: 150 nA quiescent current

-

Linear Regulator, ultra low quiescent current for retention mode TSMC 40uLPeF

- qLR-Aubrey-ref-1.62-3.63-0.55-2.5.02_TSMC_40_uLPeF is an ultra-low quiescent LDO (Linear regulator) in TSMC 40uLPeF.

-

Low Dropout Linear Regulator - TSMC 0.18µ

- The OT1103bj is a 150mA CMOS low dropout regulator designed for use in a wide variety of mixed signal device applications.

- The base design is implemented with lambda-based sizing and portable layout constructs for maximum ease of process porting.

-

Linear regulator with ultra low quiescent current for retention applications

- Very low quiescent and leakage for Low-Power

- Retention capability enables optimization of the power consumption depending on the modes and needs of the SoC

- Can supply always-on very low loads

- Can be used in stand-alone or combined with a high efficiency DCDC regulator in a RAR configuration

-

Linear Regulator for digital island

- Low dropout: 380mV of dropout at ILOAD= IMAX

- Low Bill-of-Material: optimized in density for the best trade-off for the given output current and input voltage range

- A cost-efficient solution compared to external Power Management

- Behavioral models: ease of integration in SoC and optimization of Power Management Network (PMNet) using models to verify mode transitions as well as noise propagation

-

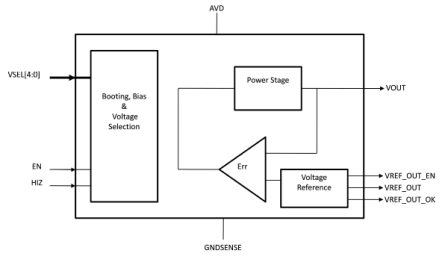

LDO linear regulator

- Low DropOut (LDO) architecture

- Low leakage for minimized shutdown current

- Programmable output voltage

- Configurable power stages for area optimization​

-

Linear Regulator for digital island

- Low Bill-of-Material: optimized in density for the best trade-off for the given output current and input voltage range

- A cost-efficient solution compared to external Power Management

- Behavioral models: ease of integration in SoC and optimization of Power Management Network (PMNet) using models to verify mode transitions as well as noise propagation

- Safe integration in the SoC thanks to transfer functions, templates and profiles included in the specification

-

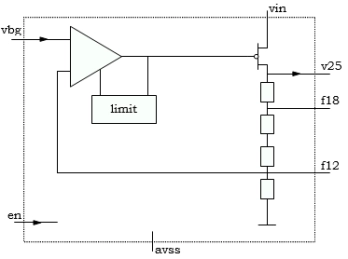

LDO linear regulator in TSMC 22ULL to supply logic and analog domains - up to 5.5 V input supply

- Low leakage current suitable for deep sleep modes

- Low quiescent current for higher efficiency at light load

- High PSRR to supply analog loads

- Support input supply voltage up to 5.5 V

-

Linear regulator with ultra low quiescent current for retention applications

- Very low quiescent and leakage for Low-Power

- Retention capability enables optimization of the power consumption depending on the modes and needs of the SoC

- Can supply always-on very low loads

- Can be used in stand-alone or combined with a high efficiency DCDC regulator in a RAR configuration

-

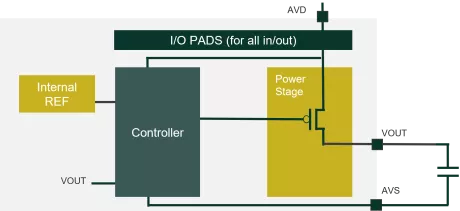

Low Drop-Out Linear Regulator

- The agileLDO is a linear Low Drop-Out voltage regulator (LDO) providing precision and programmable voltage regulation.

- The regulator architecture provides a high dynamic performance making it suitable for demanding digital applications.

- Whilst the low noise and high PSRR lends itself to powering noise-sensitive analog circuits.