LPDDR6 IP

Filter

Compare

17

IP

from

4

vendors

(1

-

10)

-

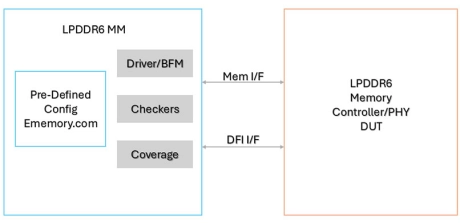

Simulation VIP for LPDDR6

- This Verification IP (VIP) is intended for modeling the upcoming JEDEC Low-Power Memory Device, LPDDR6 design specification.

- It provides a mature, highly capable compliance verification solution that supports simulation, formal analysis, and hardware acceleration platforms, making it applicable to intellectual property (IP), system-on-chip (SoC), and system-level verification.

-

-

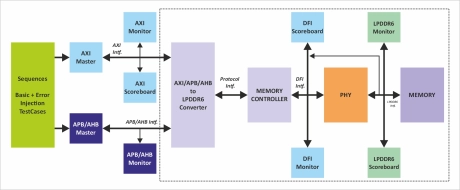

LPDDR6 Verification IP

- The LPDDR6 Verification IP provides an effective & efficient way to verify the LPDDR6 components of an IP or SoC.

- The VIP is lightweight, featuring easy-to-use plug-and-play components, so there is no impact on the design cycle time.

-

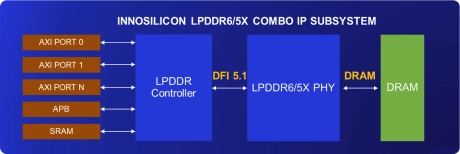

LPDDR6/5X/5 PHY V2 - TSMC N6

- The LPDDR6/5X/5 PHY IP enables ASICs, ASSPs, system-on-chips (SoCs), and system-in-package applications requiring high-performance LPDDR6, LPDDR5X, and/or LPDDR5 SDRAM interfaces operating at up to 14.4 Gbps

- With flexible configuration options, the LPDDR6/5X/5 PHY IP can be used in a variety of applications supporting LPDDR6, LPDDR5X, and/or LPDDR5 SDRAMs, precisely targeting the specific power, performance, and area (PPA) requirements of these systems

- LPDDR6 SDRAM’s combination of high bandwidth, capacity, low power, and cost effectiveness makes LPDDR6/5X/5 SDRAMs an attractive solution for traditional and new markets

- The LPDDR6/5X/5 PHY IP is designed to appeal to a variety of applications including: * Traditional mobile environments * Consumer products * Automotive solutions * Artificial intelligence * Data center applications

-

LPDDR6/5X/5 PHY V2 - TSMC N5A for Automotive, ASIL B Random, AEC-Q100 Grade 2

- The LPDDR6/5X/5 PHY IP enables ASICs, ASSPs, system-on-chips (SoCs), and system-in-package applications requiring high-performance LPDDR6, LPDDR5X, and/or LPDDR5 SDRAM interfaces operating at up to 14.4 Gbps

- With flexible configuration options, the LPDDR6/5X/5 PHY IP can be used in a variety of applications supporting LPDDR6, LPDDR5X, and/or LPDDR5 SDRAMs, precisely targeting the specific power, performance, and area (PPA) requirements of these systems

- LPDDR6 SDRAM’s combination of high bandwidth, capacity, low power, and cost effectiveness makes LPDDR6/5X/5 SDRAMs an attractive solution for traditional and new markets

- The LPDDR6/5X/5 PHY IP is designed to appeal to a variety of applications including: * Traditional mobile environments * Consumer products * Automotive solutions * Artificial intelligence * Data center applications

-

LPDDR6/5X/5 PHY V2 - TSMC N5

- The LPDDR6/5X/5 PHY IP enables ASICs, ASSPs, system-on-chips (SoCs), and system-in-package applications requiring high-performance LPDDR6, LPDDR5X, and/or LPDDR5 SDRAM interfaces operating at up to 14.4 Gbps

- With flexible configuration options, the LPDDR6/5X/5 PHY IP can be used in a variety of applications supporting LPDDR6, LPDDR5X, and/or LPDDR5 SDRAMs, precisely targeting the specific power, performance, and area (PPA) requirements of these systems

- LPDDR6 SDRAM’s combination of high bandwidth, capacity, low power, and cost effectiveness makes LPDDR6/5X/5 SDRAMs an attractive solution for traditional and new markets

- The LPDDR6/5X/5 PHY IP is designed to appeal to a variety of applications including: * Traditional mobile environments * Consumer products * Automotive solutions * Artificial intelligence * Data center applications

-

LPDDR6/5X/5 PHY V2 - TSMC N4P

- The LPDDR6/5X/5 PHY IP enables ASICs, ASSPs, system-on-chips (SoCs), and system-in-package applications requiring high-performance LPDDR6, LPDDR5X, and/or LPDDR5 SDRAM interfaces operating at up to 14.4 Gbps

- With flexible configuration options, the LPDDR6/5X/5 PHY IP can be used in a variety of applications supporting LPDDR6, LPDDR5X, and/or LPDDR5 SDRAMs, precisely targeting the specific power, performance, and area (PPA) requirements of these systems

- LPDDR6 SDRAM’s combination of high bandwidth, capacity, low power, and cost effectiveness makes LPDDR6/5X/5 SDRAMs an attractive solution for traditional and new markets

- The LPDDR6/5X/5 PHY IP is designed to appeal to a variety of applications including: * Traditional mobile environments * Consumer products * Automotive solutions * Artificial intelligence * Data center applications

-

LPDDR6/5X/5 PHY V2 - TSMC N4C

- The LPDDR6/5X/5 PHY IP enables ASICs, ASSPs, system-on-chips (SoCs), and system-in-package applications requiring high-performance LPDDR6, LPDDR5X, and/or LPDDR5 SDRAM interfaces operating at up to 14.4 Gbps

- With flexible configuration options, the LPDDR6/5X/5 PHY IP can be used in a variety of applications supporting LPDDR6, LPDDR5X, and/or LPDDR5 SDRAMs, precisely targeting the specific power, performance, and area (PPA) requirements of these systems

- LPDDR6 SDRAM’s combination of high bandwidth, capacity, low power, and cost effectiveness makes LPDDR6/5X/5 SDRAMs an attractive solution for traditional and new markets

- The LPDDR6/5X/5 PHY IP is designed to appeal to a variety of applications including: * Traditional mobile environments * Consumer products * Automotive solutions * Artificial intelligence * Data center applications

-

LPDDR6/5X/5 PHY V2 - TSMC N3P

- The LPDDR6/5X/5 PHY IP enables ASICs, ASSPs, system-on-chips (SoCs), and system-in-package applications requiring high-performance LPDDR6, LPDDR5X, and/or LPDDR5 SDRAM interfaces operating at up to 14.4 Gbps

- With flexible configuration options, the LPDDR6/5X/5 PHY IP can be used in a variety of applications supporting LPDDR6, LPDDR5X, and/or LPDDR5 SDRAMs, precisely targeting the specific power, performance, and area (PPA) requirements of these systems

- LPDDR6 SDRAM’s combination of high bandwidth, capacity, low power, and cost effectiveness makes LPDDR6/5X/5 SDRAMs an attractive solution for traditional and new markets

- The LPDDR6/5X/5 PHY IP is designed to appeal to a variety of applications including: * Traditional mobile environments * Consumer products * Automotive solutions * Artificial intelligence * Data center applications

-

LPDDR6/5X/5 PHY - TSMC N3P

- The LPDDR6/5X/5 PHY IP enables ASICs, ASSPs, system-on-chips (SoCs), and system-in-package applications requiring high-performance LPDDR6, LPDDR5X, and/or LPDDR5 SDRAM interfaces operating at up to 14.4 Gbps

- With flexible configuration options, the LPDDR6/5X/5 PHY IP can be used in a variety of applications supporting LPDDR6, LPDDR5X, and/or LPDDR5 SDRAMs, precisely targeting the specific power, performance, and area (PPA) requirements of these systems

- LPDDR6 SDRAM’s combination of high bandwidth, capacity, low power, and cost effectiveness makes LPDDR6/5X/5 SDRAMs an attractive solution for traditional and new markets

- The LPDDR6/5X/5 PHY IP is designed to appeal to a variety of applications including: * Traditional mobile environments * Consumer products * Automotive solutions * Artificial intelligence * Data center applications