LPDDR Interface IP

Filter

Compare

155

IP

from

18

vendors

(1

-

10)

-

SMIC 55nm LL LPDDR interface for DRAM application

- LPDDR interface for DRAM application;

- SMIC 55nm Logic Low Leakage 1P10M Salicide 1.2V/1.8V/2.5V Process;

- Cell Size (Width * height) 35um * 174um with DUP stagger bonding pads;

- Work voltage: 1.8V;

-

SMIC 65nm LL LPDDR interface for mobile-DDR application

- LPDDR interface for mobile-DDR application;

- Cell Size (Width * height) 35um * 174um with DUP stagger bonding pads;

- Work voltage: 1.8V power;

- Support MDDR, datarate up to 400Mbps;

-

SMIC 65nm LL SSTL_18/ SSTL_2/ LPDDR/ LVTTL COMBO interface for DRAM application

- SSTL_18/ SSTL_2/ LPDDR/ LVTTL COMBO interface for DRAM application;

- SMIC 65nm Logic Low Leakage 1P10M Salicide 1.2V/1.8V/2.5V Process;

- Cell Size (Width * height) (35~80)um * 211um with DUP stagger bonding pads;

- Work voltage: 1.8V/2.5V/3.3V;

-

SMIC 55nm LL SSTL_18/ SSTL_2/ LPDDR/ LVTTL COMBO interface for DRAM application

- SSTL_18/ SSTL_2/ LPDDR/ LVTTL COMBO interface for DRAM application;

- 2).Suppport ONFI3.1/Toggle2.0 interface;

- 3).SMIC 55nm Logic Low Leakage Salicide 1.2V/1.8V/2.5V Process;

- 4).Cell Size (Width * height) 35um * 325um with DUP stagger bonding pads;

-

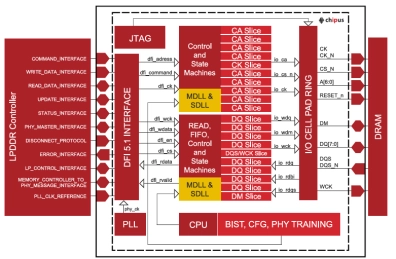

LPDDR4/4x/5/5x PHY

- Supports JEDEC SDRAM standards including LPDDR4 (1.1V), LPDDR4x (0.6V), LPDDR5/5x (0.5V)

- Supports data rates up to 4,266 Mbps LPDDR4/LPDDR5 and up to 8,533 Mbps LPDDR5x

- Support for 16, 32 and 64-bit operation

-

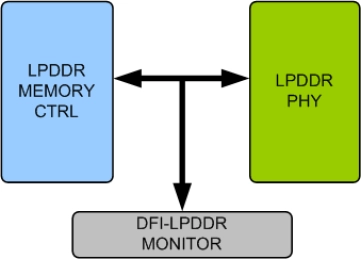

LPDDR DFI Verification IP

- Compliant with DFI version 2.0 or higher Specifications.

- Supports LPDDR devices compliant with JEDEC LPDDR SDRAM Standard JESD209A-1.pdf and JESD209B.pdf

- Supports all Interface Groups.

- Supports Write Transactions with Data mask

-

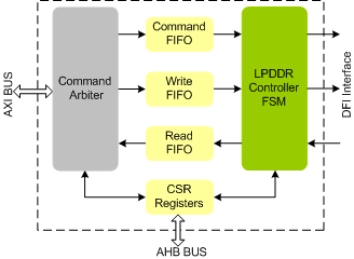

LPDDR Controller IIP

- Supports LPDDR protocol standard and JESD209A-1 and JESD209B Specification

- Compliant with DFI version 2.0 or higher Specification.

- Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transcations for AXI write and read channels

-

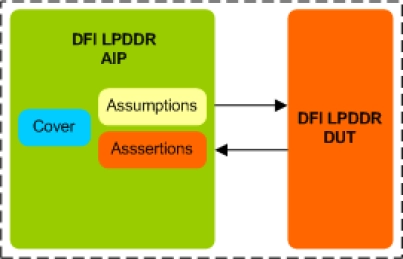

LPDDR DFI Assertion IP

- Specification Compliance

- Compliant with DFI version 2.0 or higher Specifications.

- Supports LPDDR devices compliant with JEDEC LPDDR SDRAM Standard JESD209A-1.pdf and JESD209B.pdf.

- Supports all Interface Groups.

-

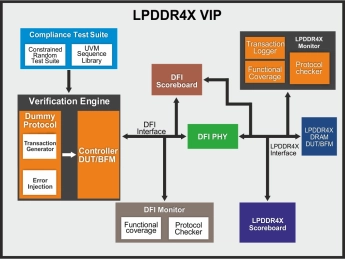

LPDDR4X Verification IP

- Compliant with JEDEC LPDDR4X Specification version JESD209-4-1.

- Supports LPDDR4X memory devices from all leading vendors.

- Supports multiple densities: 4Gb to 32Gb.

- Supports all lpddr4x ODT CA/CS/CKT control via MRS register

-

LPDDR Controller

- Memory controller interface complies with DFI standard up to 5.0

- Application-optimized configurations for fast time to delivery and lower risk

- Sideband and in-line SEC/DED ECC

- Supports advanced RAS features including error scrubbing, parity, etc.

- Compliant to LPDDR5/4X/4/3 protocol memories

- Priority per command on Arm®AMBA® 4 AXI, AMBA 3 AXI