Intrinsic-ID IP

Filter

Compare

24

IP

from

10

vendors

(1

-

10)

-

PUF FPGA-Xilinx Premium with key wrap

- Proven “Soft” PUF implementation for AMD/Xilinx FPGAs, part of the FPGA configuration file

- Offers FPGA users a cryptographic technology to secure their own keys and to authenticate devices and communications between them on networks.

- Enables remote “brownfield” installation of hardware-based security

-

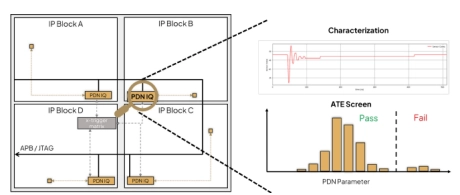

On-Die PDN Analyzer for Transistor-Level Visibility and Telemetry

- The Aeonic Insight™ PDN IQ is an in-situ, on-die PDN (Power Delivery Network) analyzer providing transistorlevel PDN telemetry at nanosecond scale.

- The telemetry provided can be applied across the silicon lifecycle to optimize power, performance, and reliability.

- PDN IQ can be used to characterize V-F curves to develop an optimal setpoint to balance power and performance.

-

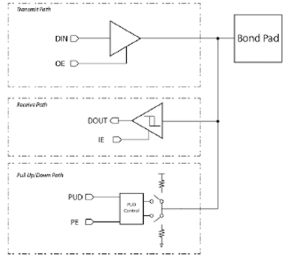

Three-Speed Inline Library with Open Drain I/0 in TSMC 22nm

- A TSMC 22nm Inline, Flip Chip compatible library with three-speed GPIOs and I2C compliant ODIO.

- This silicon-proven, flip chip library in TSMC 22nm boasts three variants of GPIOs and one ODIO.

- All GPIO and ODIO cells have NS and EW orientation.

-

PUF FPGA-Xilinx Base

- Proven “Soft” PUF implementation for AMD/Xilinx FPGAs, part of the FPGA configuration file

- Offers FPGA users a cryptographic technology to secure their own keys and to authenticate devices and communications between them on networks.

- Enables remote “brownfield” installation of hardware-based security

- Offers key provisioning, wrapping, and unwrapping to enable secure key storage across the supply chain and for the lifetime of the device

-

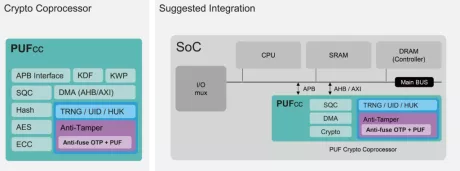

TLS 1.3 Compliant Crypto Coprocessor

- NIST CAVP certified and OSCCA standard compliant crypto engine suite

- Includes private/public key ciphers, message authentication code, hashes, and key derivation

- Key wrapping function for the secure export of keys

- Public-key coprocessor for digital signatures and key agreements over elliptic/Edward curves

-

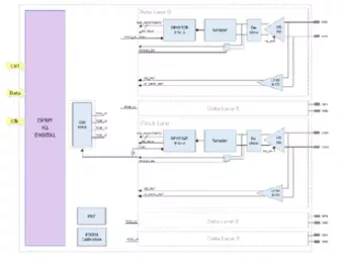

MIPI D-PHY Rx IP, Silicon Proven in GF 55LP

- Compliant to MIPI Alliance Standard for D-PHY specification Version 1.2

- Supports standard PPI interface compliant to MIPI Specification

- Supports synchronous transfer at high-speed mode with a bit rate of 80-2500 Mb/s

- Supports asynchronous transfer at low power mode with a bit rate of 10 Mb/s

-

VDAC

- ? 10-bit Resolution

- ? 1 to 300 MSPS Update Rate

- ? One to six channel Video DAC

- ? Programmable output swing from 0.56V to 1.3V

-

MIPI D-PHY Rx IP, Silicon Proven in TSMC 40LP

- Compliant to MIPI Alliance Standard for D-PHY specification Version 1.2

- Supports standard PPI interface compliant to MIPI Specification

- Supports synchronous transfer at high-speed mode with a bit rate of 80-2500 Mb/s

- Supports asynchronous transfer at low power mode with a bit rate of 10 Mb/s

-

MIPI D-PHY Rx IP, Silicon Proven in TSMC 16FFC

- Compliant to MIPI Alliance Standard for

- D-PHY specification Version 1.2

- Supports standard PPI interface compliant to MIPI Specification

- Supports synchronous transfer at high speed mode with a bit rate of 80-2500 Mb/s

-

256 8-bit-MAC DSP core

- High performance vector signal processing and efficient control code processing

- 256 8-bit macs, or 128 16-bit macs, or 32-bit macs per cycle

- Flexible vector permute operations

- Maskable vector lanes