I/O library TowerJazz 65nm IP

Filter

Compare

701

IP

from

28

vendors

(1

-

10)

-

VeriSilicon IBM 65nm 1.0V/2.5V VPPIO_01 IO Library

- IBM 65nm 10sf 1.0/2.5V process

- Provides 6.5V power supply IO pads for OTP application, resisting instantaneous high voltage zap

- Supports Device Under Pad (DUP)

- Direct interface with Aragio IO library

-

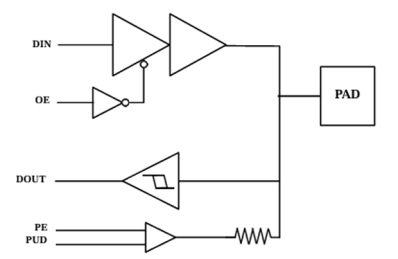

High-Speed 3.3V I/O library with 8kV ESD Protection in TSPCo 65nm

- A 3.3V wirebond I/O library with 8kV HBM ESD protection, a 1.2Gbps LVDS, GPIO, and I2C compliant ODIO in an ultra-small footprint.

- This library ensures robust reliability in challenging environments, with capabilities including 8kV HBM, 500V CDM, and a robust 2kV IEC 61000-4-2 system stress capability.

- Its compact footprint makes it ideal for applications where size is critical.

-

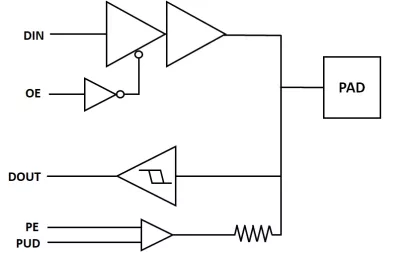

Wirebond Digital and Analog Library in TSMC 65nm

- A mixed Digital and Analog Library, compatible with I2C and I3C Protocols.

- This library is a mixed Digital and Analog library built for the TSMC 65nm process.

- It is based around a Fail-Safe General Purpose Input/Output (FSGPIO) cell that is compatible with both I2C and I3C protocols.

-

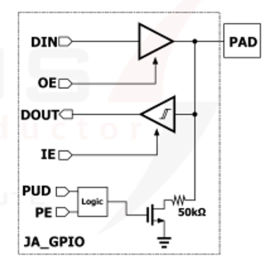

Multi-Voltage GPIO 5V ODIO and Analog/RF I/Os in TSMC 65nm

- Key attributes of this IO library include dual independent IO supply rails (1.0V-3.3V 3.3V) and power-on-control (POC) to place IOs in HiZ during power-down.

- The GPIO cell can be configured as input, output or open-drain with a Schmitt trigger input and optional internal 55K ohm pull-up or pull-down resistor.

- Cells for two independent IO supplies, core power, ground and isolated ground with built-in ESD are included.

-

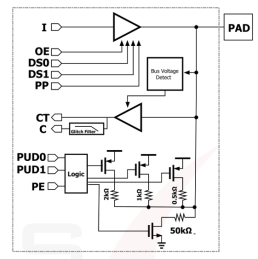

2.5V GPIO with 2Gbps LVDS RX TX and Analog Cell in GlobalFoundries 65nm LPe

- A GlobalFoundries 65nm LPE Wirebond I/O library with 2.5V GPIO, 2Gbps LVDS TX RX and 2.5V Analog/RF cell with associated ESD.

- A key attribute of this silicon-proven library include dual selectable drive strengths and independent input & output enable / disable.

- The GPIO cell can be configured as input, output or open-drain with a Schmitt trigger input and selectable internal 60K ohm pull-up or pull-down resistor.

-

DDR3/2 PHY - TSMC 40LP25

- When combined with a Synopsys DDR memory or protocol controller and verification IP, Synopsys provides a complete DDR3/2 interface IP solution

- Scalable architecture that supports the speed range from DDR2-667 up to DDR3-2133

- Support for DDR3L (1.35V DDR3)

- Support for DDR2 and DDR3 DIMMs