HSSTP IP

Filter

Compare

2

IP

from

2

vendors

(1

-

2)

-

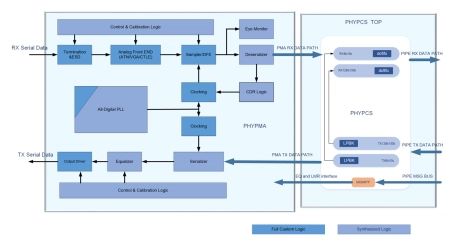

Multi-Standard SerDes PHY

- Configurable parallel data rate of 8 /10 / 16 / 20 / 32 / 40 / 64 / 80

- Input reference 5MHz to support 2.5/5/10G data rates

- Tight control over termination resistor (~50 Ohm) with on chip calibration

- Tight skew control of 1UI between lanes of the PMA

- Multi-tap Tx Finite Impulse Response (FIR) equalizer with multi-level de-emphasis

-

Multi-Rate Serdes IP Solution

- YouPHY-Serdes provides 2.5-32Gbps multi-rate SERDES IP which is designed for smooth integration of Multiple SERDES lanes demonstrate good performance class performance, area and power.

- The programmable PHY supports major standards such as PCIe Gen 4.0/3.0/2.0/1.0, USB 3.1/3.0, XAUI, SATA Gen 3.0/2.0/1.0, CEI-11G-LR, 10GBase-KX4, JESD204B, SGMII/QSGMII, RAPID I/O, HSSTP (Trace Port), V-By-One, DisplayPort and HMC.