HSIC PHY IP

Filter

Compare

9

IP

from

6

vendors

(1

-

9)

-

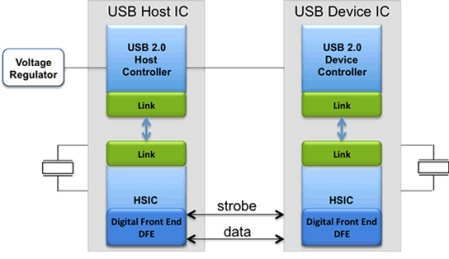

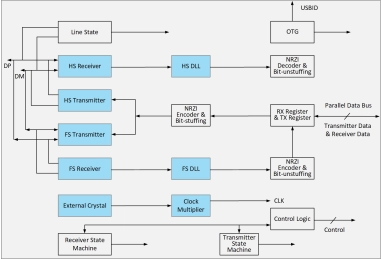

High Speed Inter-CHIP USB 2.0 PHY

- High-Speed 480Mbps data rate only

- Source-synchronous serial interface

- No power consumed unless a transfer is in progress.

- Maximum trace length of 10cm

-

USB 2.0 Hi-Speed OTG Controller Subsystem w/AHB Interface Supporting HSIC (config. as Device only or Full Speed only)

- Configuration options to maximize performance and minimize CPU interrupts

- Flexible parameters enable easy integration into low and high-latency systems

- Transfer- or transaction-based processing of USB data based on system requirements

- Configurable data buffering options to fine-tune performance/ area trade-offs

-

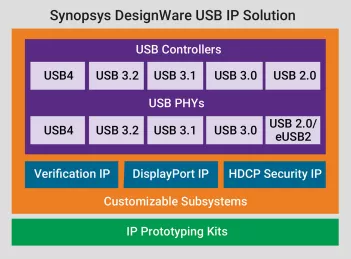

USB2.0 PHY(HSIC/Host/Device/OTG/Hub)/ eUSB PHY

- USB is the ubiquitous interconnect standard of choice for a wide range of computing and consumer applications

- Innosilicon provides a comprehensive set of software drivers to support commonly used USB peripherals

- In addition, our established USB ecosystem—comprising USB silicon suppliers, design IP houses, and verification and testing vendors—helps reduce development and production costs for USB host and peripheral manufacturers

-

SuperSpeed USB 3.0 Host Controller Supporting SSIC and HSIC

- Supports SuperSpeed USB power savings modes, Uniform Power Format (UPF) and dual power rails

- Lowers overall system power by design

- Configurable data buffering options to fine-tune performance/area trade-offs

- Host supports SuperSpeed, High-Speed, Full-Speed, and Low-Speed operation

-

SuperSpeed USB 3.0 Dual Role Device Controller, Configurable for SSIC and HSIC

- Supports SuperSpeed USB power savings modes, Uniform Power Format (UPF) and dual power rails

- Lowers overall system power by design

- Configurable data buffering options to fine-tune performance/area trade-offs

- Host supports SuperSpeed, High-Speed, Full-Speed, and Low-Speed operation

-

SuperSpeed USB 3.0 Device Controller Supporting SSIC and HSIC

- Supports SuperSpeed USB power savings modes, Uniform Power Format (UPF) and dual power rails

- Lowers overall system power by design

- Configurable data buffering options to fine-tune performance/area trade-offs

- Host supports SuperSpeed, High-Speed, Full-Speed, and Low-Speed operation

-

AXI USB 2.0 Device Controller

- AXI-4 based host Interface. AXI-4 Lite for Slave Interface and optional AXI-4 Master interface for DMA mode

- Supports High Speed and Full Speed USB 2.0 specification

- Supports high speed, high bandwidth isochronous transactions

- Supports up to eight endpoints, including one control endpoint 0. Endpoints 1 to 7 can be bulk, interrupt, or isochronous and are individually configurable

-

Simulation VIP for USB

- Configurations

- Gen2x2, Gen1x2, Gen2x1, and Gen1x1

- Supported DUT Models

- Host, Device and PHY Model for USB2 or USB3

-

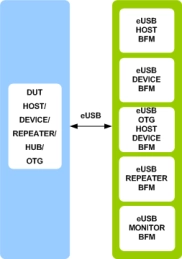

eUSB Verification IP

- eUSB

- Compatible with Embedded USB2 (eUSB2) Physical Layer Supplement to the USB Revision 2.0 Specification Rev.1.1.

- Fully compliant to the USB2.0 layer architecture with the following features:

- Supports high-speed, full-speed, and low-speed operation.