HBM3 IP

Filter

Compare

46

IP

from

10

vendors

(1

-

10)

-

Simulation VIP for HBM3

- Speed (MHz)

- Clock: 1800MHz; data rate: 7.2Gbps/pin

- Mode Registers

- All 16 mode registers are supported

-

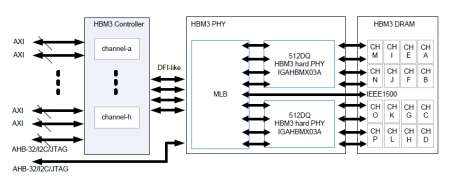

TSMC CLN7FF HBM3 PHY

- IGAHBMX03A is a HBM3 (High Bandwidth Memory) PHY IP compliant to the JEDEC HBM3 DRAM Specification Rev 0.95.

- Built on TSMC 7nm process node, it supports data rate up to 7200 Mbps per data pin with DFI 1:4 clock frequency ratio (controller clock : WCK = 1:4).

-

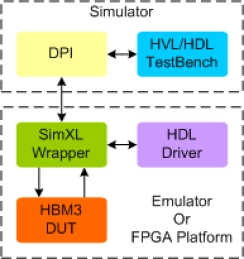

HBM3 Synthesizable Transactor

- Supports 100% of HBM3 protocol draft JEDEC specification version 1.1.

- Supports all the HBM3 commands as per the specs.

- Supports programmable clock frequency of operation.

- Support all types of timing and protocol violation detection.

-

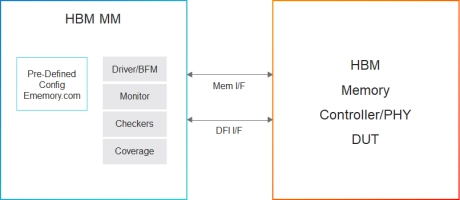

HBM3 Memory Model

- Supports HBM3 memory devices from all leading vendors.

- Supports 100% of HBM3 protocol draft JEDEC specification version 1.1.

- Supports all the HBM3 commands as per the specs.

- Supports programmable clock frequency of operation.

-

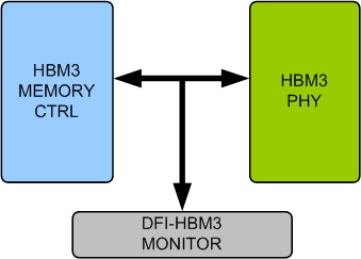

HBM3 DFI Verification IP

- Compliant with DFI version 4.0 or 5.0 Specifications.

- DFI-HBM3 Applies to :

- HBM3 protocol draft JEDEC specification version 0.93.

- Supports for Read data bus inversion.

-

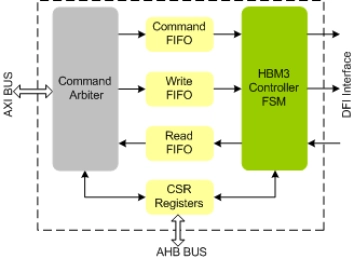

HBM3 Controller IIP

- Supports HBM3 protocol standard draft JEDEC specification version 1.02.

- Compliant with DFI version 4.0 or 5.0 Specification.

- Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transactions for AXI write and read channels

-

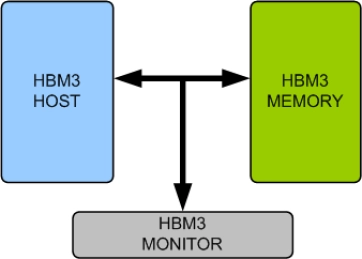

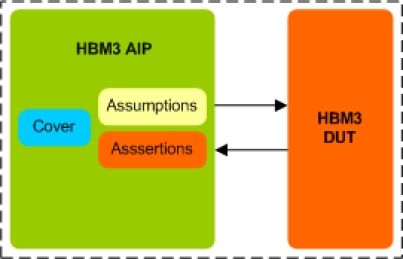

HBM3 Assertion IP

- Specification Compliance

- Supports HBM3 memory devices from all leading vendors.

- Supports 100% of HBM3 protocol JEDEC draft specification version 1.1.

- Supports all the HBM3 commands as per the specs.

-

HBM3 PHY

- Advanced clocking architecture minimizes clock jitter

- DFI PHY Independent Mode for initialization and training

- IEEE 1500 interface, Memory BIST feature, and loop-back function

- Supports lane repair

- Designed for optimized interposer routing

-

HBM3 PHY V2 - TSMC N3E

- Supports 2.5D-based JEDEC standard HBM3 DRAMs with data rates up to 9600 Mbps

- 16 independent 64-bit memory channels

- Pseudo-channel operation supported to enable up to 32 32-bit pseudo-channels with 1024-bit PHY

- Supports up to 4 trained frequencies with <5us switching time

-

HBM3 PHY V2 (Hard) - TSMC N3P

- Supports 2.5D-based JEDEC standard HBM3 DRAMs with data rates up to 9600 Mbps

- 16 independent 64-bit memory channels

- Pseudo-channel operation supported to enable up to 32 32-bit pseudo-channels with 1024-bit PHY

- Supports up to 4 trained frequencies with <5us switching time