DisplayHDR IP

Filter

Compare

166

IP

from

41

vendors

(1

-

10)

-

HDCP 2 on HDMI / DisplayPort Embedded Security Module Firmware (generation 3)

- Complete, self-contained security modules with hardware Root of Trust

- Transmitter (TX), Receiver (RX) and Repeater (Rep) solutions

- Silicon-proven. Widely deployed. Certified.

- Compliant with the latest HDCP 2.3 content protection standard (backwards compatible with HDCP 2.2)

-

4-port Receiver/Transmitter/Repeater HDCP 2.3 on HDMI 2.0 and/or DisplayPort 2.0/1.4 ESM (generation 3)

- The Multiport/Multiprotocol HDCP 2.2/2.3 Embedded Security Modules (ESMs) are autonomous modules that provide designers with complete and robust transmitter (TX), receiver (RX) and repeater (Rep) implementations of the HDCP 2.3 content protection technology over HDMI 2.1/2.0, DisplayPort 2.0/1.4, and USB 3.x Type-C wired connections.

- These solutions help designers shorten development cycles and fully meet the stringent security requirements of the DCP LLC licensing authority.

-

2-port Receiver/Transmitter/Repeater HDCP 2.3 on HDMI 2.0 and/or DisplayPort 2.0/1.4 ESM (generation 3)

- Complete, self-contained security modules with hardware Root of Trust

- Transmitter (TX), Receiver (RX) and Repeater (Rep) solutions

- Silicon-proven. Widely deployed. Certified.

- Compliant with the latest HDCP 2.3 content protection standard (backwards compatible with HDCP 2.2)

-

1-port Receiver/Transmitter HDCP 2.3 on HDMI 2.0 or DisplayPort 1.4/2.0 ESM (generation 3)

- The Multiport/Multiprotocol HDCP 2.2/2.3 Embedded Security Modules (ESMs) are autonomous modules that provide designers with complete and robust transmitter (TX), receiver (RX) and repeater (Rep) implementations of the HDCP 2.3 content protection technology over HDMI 2.1/2.0, DisplayPort 2.0/1.4, and USB 3.x Type-C wired connections.

- These solutions help designers shorten development cycles and fully meet the stringent security requirements of the DCP LLC licensing authority.

-

DisplayPort Link Policy Maker

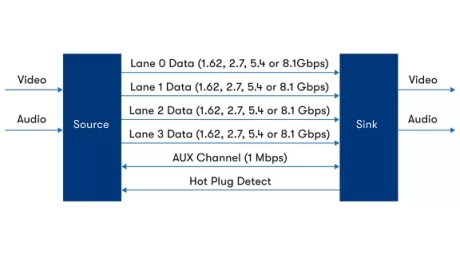

- The DisplayPort Link Policy Maker (LPM) is a DisplayPort 1.4/2.0 compliant software stack that manages and controls the DisplayPort serial link and AUX channel communications.

- The software provides for enumeration and configuration of the source and sink devices, adaptive training of the DisplayPort link, video stream allocation and transmission, AUX channel traffic management and handling of all HPD (Hot Plug Detect) events.

-

DisplayPort Intel® FPGA IP Core

- Intel now offers a fully VESA-compliant DisplayPort Intel® FPGA IP core v1.4

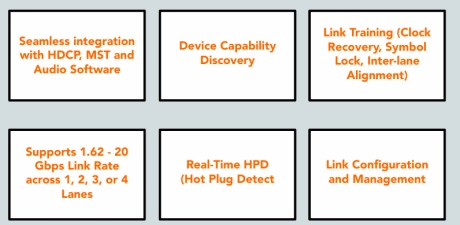

- The DisplayPort IP core is found prevalently in many video-related products servicing a wide variety of applications and has the following features:

-

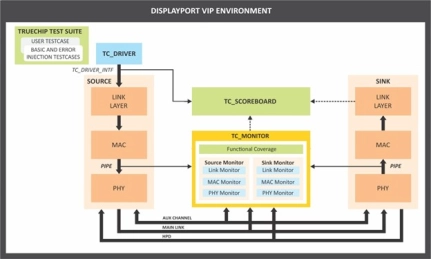

DisplayPort - Validates high-quality video and audio transmission for displays

- DisplayPort is a high-performance digital display interface designed for connecting computers, monitors, and other video devices. It supports high-definition and ultra-high-definition displays, offering top-tier video and audio transmission.

- In Verification IP (VIP), DisplayPort ensures the accurate functioning of display controllers, validating the transmission of video and audio data. VIP verifies compliance with DisplayPort standards, ensuring seamless integration with a wide range of devices.

-

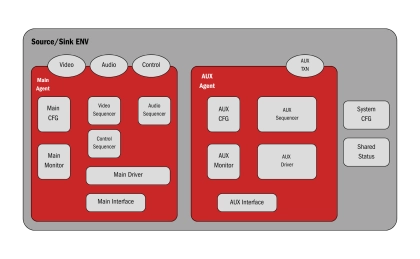

Simulation VIP for DisplayPort

- Device Support

- Source, Sink, Link Training-Tunable PHY Repeater (LTTPR/retimer)

- Main Link Interface

- Serial, Parallel (10-bit, 20-bit, 40-bit)

-

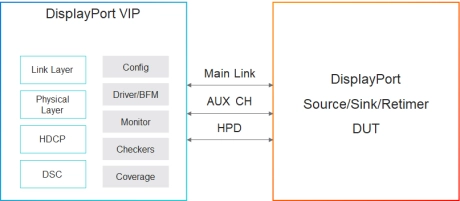

DisplayPort 2.1 Verification IP

- Supports Isochronous transport services over the Main-Link.

- Capable Link and device management services over the AUX_CH.

- Can handle AUX transaction to access the DisplayPort Configuration Data (DPCD) address.

- Capable of handling multi stream packet and single stream packet data transmission.

-

DisplayPort 2.0 Verification IP

- Fully compliant to VESA DisplayPort standard 2.0 Specification

- Supports High Bandwidth Digital Content Protection System Version 1.4, 2.2 and 2.3.

- Supports Multi-Stream transport (MST)

- Supports Link Training(LT) tunable PHY Repeaters (LTTPR)