DDR4 Memory IP

Filter

Compare

180

IP

from

23

vendors

(1

-

10)

-

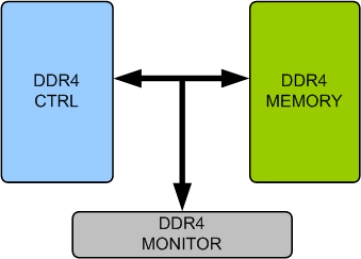

DDR4 Memory Model

- Supports DDR4 memory devices from all leading vendors.

- Supports 100% of DDR4 protocol standard JESD79-4, JESD79-4A, JESD79-4A_r2, JESD79-4B, JESD79-4Cand JESD79-4D(Draft).

- Supports all the DDR4 commands as per the specs.

- Supports up to 16GB device density.

-

DDR3L/ LPDDR4/ DDR4 PHY IP - 1866Mbps (Silicon Proven in UMC 28HPC+)

- Supported DRAM type: DDR3L/DDR4/LPDDR4

- Maximum controller clock frequency of 400MHz resulting in maximum DRAM data rate of 1866Mbps

- Interface: SSTL135/POD12/LVSTL

- Data path width scales in 32-bit increment

-

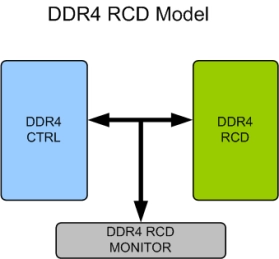

DDR4 RCD Memory Model

- Supports DDR4 RCD devices from all leading vendors. Supports 100% of DDR4 RCD protocol standard JESD82-31A.

- Supports all speed grades as per specification. Quickly validates the implementation of the DDR4 RCD standard JESD82-31A.

- Supports DDR4 command and address bus transmission as per DDR4 standard JESD79-4C.

- Supports parity.

-

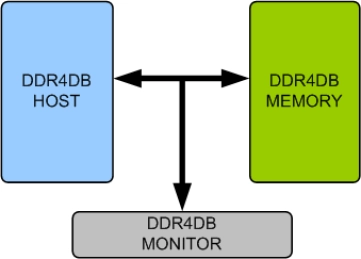

DDR4 DB Memory Model

- Supports DDR4 DB devices from all leading vendors.

- Supports 100% of DDR4 DB protocol standard JESD82-32A and DDR4 Protocol standard JESD79-4B.

- Supports all the DDR4 DB commands as per the specs.

- Supports all speed grades as per specification.

-

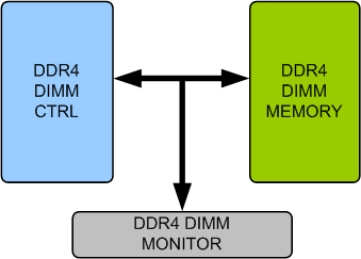

DDR4 DIMM Memory Model

- Supports DDR4 DIMM memory devices from all leading vendors.

- Supports 100% of DDR4 DIMM protocol standard.

- Supports DDR4 UDIMM, RDIMM and LRDIMM types.

- Supports all the DDR4 DRAM features.

-

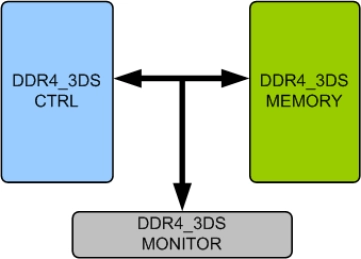

DDR4 3DS Memory Model

- Supports DDR4 3DS memory devices from all leading vendors.

- Supports 100% of DDR4 3DS protocol standard JESD79-4-1, JESD79-4-1A and JESD79-4-1B.

- Supports all the DDR4 3DS commands as per the specs.

- Supports up to 16GB device density.

-

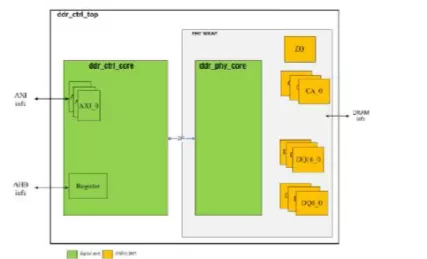

DDR4 / DDR3/ DDR3L / LPDDR4 Memory Controller IP optimized for low latency

- Support DDR3 / DDR3L / DDR4/ 3DS DDR4/ LPDDR4 / MRAM

- Support x8/x16/x32 DRAM data bus configuration (programmable)

- Support Multi-Ranks DRAM configuration

- DDR base on DFI spec 4.0 compliant.

-

DDR4 IO for memory PHY, 3200Mbps on SMIC 40nm

- The DDR4 IO is used to transfer the Command/Address/Clk and Data between the memory controller PHY and the DRAM device

- The TX is designed to send information from PHY to DRAM and RX is designed to receive information which is from DRAM.

-

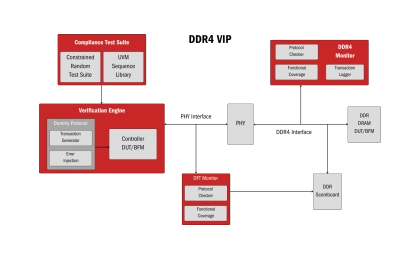

DDR4 Controller - Validates memory compliance, optimizes performance, ensures reliability

- The DDR4 Memory Controller Verification IP ensures compliance with DDR4 standards, validating high-speed data transfer, read/write operations, and error correction. It provides automated testing, advanced debugging tools, and scalability for complex memory systems.

- Designed for versatile applications, this IP optimizes performance in gaming consoles, data centers, AI systems, networking devices, and more. It ensures memory reliability, efficiency, and scalability across industries, accelerating time-to-market for DDR4-based products

-

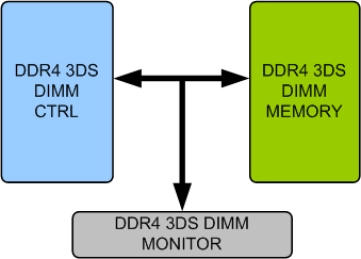

DDR4 3DS DIMM Memory Model

- Supports DDR4 3DS DIMM memory devices from all leading vendors.

- Supports 100% of DDR4 3DS DIMM protocol standard JESD79-4-1,JESD79-4-1A.

- Supports all the DDR4 3DS RDIMM and LRDIMM types.

- Supports up to 16GB device density.