DDR2 memory controller IP

Filter

Compare

26

IP

from

14

vendors

(1

-

10)

-

Avalon Multi-port DDR2 Memory Controller

- 200 / 333 MHz (400/666 Mbps) Cyclone/Stratix DDR2 memory performance

- DDR2 Memory Devices

- From 1 to 16 Avalon-MM local bus port interfaces

- Memory bandwidth utilization in excess of 95%

-

-

High Performance DDR 3/2 Memory Controller IP

- Supports DDR3/DDR2 SDRAM

- 16 bits width DDR2/DDR3 SDRAM Interface

- Memory Clock up to 462MHz, DFI Clock up to 462MHz

- Support DDR2 667/800/1066 and DDR3 667/800/1066/1333/1600/1866

-

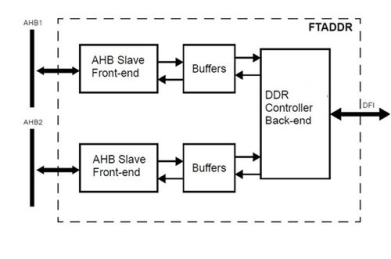

Fault Tolerant DDR2/DDR3/DDR4 Memory controller

- FTADDR is a memory controller for DDR2,DDR3 and DDR4 SDRAM memory devices.

- It uses a strong error correction code to achieve exceptional fault tolerance

-

High-Performance Memory Controller II SDRAM Intel® FPGA IP Core

- The High-Performance Memory Controller II SDRAM Intel FPGA IP core handles the complex aspects of using DDR, DDR2, and DDR3 SDRAM at speeds up to 933 MHz

- The intellectual property (IP) core initializes the memory devices, manages SDRAM banks, translates read-and-write requests from the local interface into all the necessary SDRAM command signals, and performs command and data reordering.

-

DO-254 DDR Memory Controller 1.00a

- DDR, DDR2, DDR3, and LPDDR (Mobile DDR) memory standards support

- Up to 800 Mb/s (400 MHz double data rate) performance

- Up to four MCB cores in a single Spartan-6 device

- Configurable dedicated multi-port user interface to FPGA logic

-

-

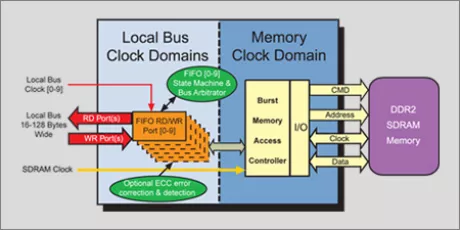

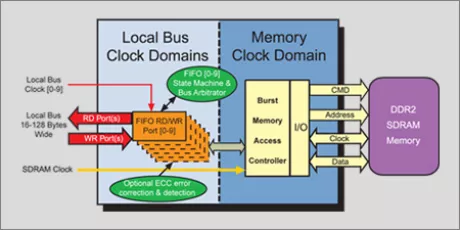

Streaming Multi-port SDRAM Memory Controller

- 200/333 MHz (400/666 Mbps) Cyclone / Stratix memory performance

- SDR, DDR, DDR2, and Mobile DDR SDRAM memory devices

- Up to 10 native RD or WR ports

- Memory data width: 8/16/32/64-bit

-

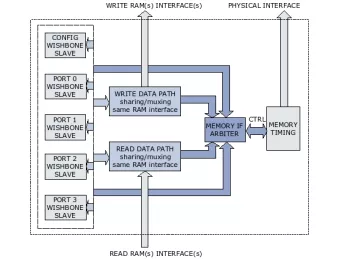

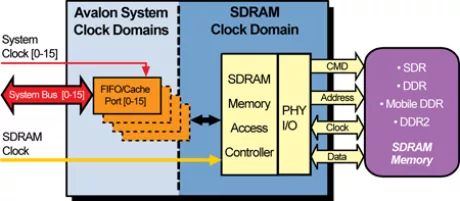

Avalon Multi-port SDRAM Memory Controller IP Core

- 200 / 333 MHz (400/666 Mbps) Cyclone / Stratix DDR2 memory performance

- SDR, DDR, DDR2 and Mobile DDR SDRAM Memory Devices

- From 1 to 16 Avalon-MM local bus port interfaces

- Memory bandwidth utilization in excess of 95%

-

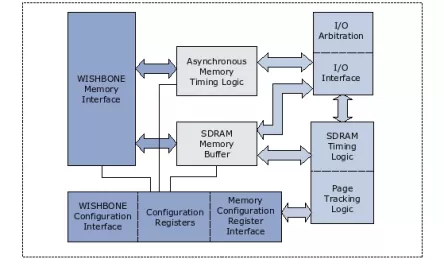

DDR and DDR2 SDRAM Controller Intel® FPGA IP Core

- The DDR and DDR2 SDRAM controllers handle the complex aspects of using DDR and DDR2 SDRAM—initializing the memory devices, managing SDRAM banks, and keeping the devices refreshed at appropriate intervals

- The controllers translate read-and-write requests from the local interface into all the necessary SDRAM command signals.