Capture Engine IP

Filter

Compare

15

IP

from

10

vendors

(1

-

10)

-

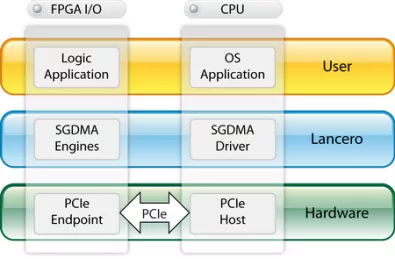

Lancero Scatter-Gather DMA Engine for PCI Express

- PCIe I/O performance: 200 MB/s x1 Gen 1 up to 3360 MB/s x8 Gen 2

- Easily connect logic and high-speed I/O peripherals to PCI Express

- Target Bridge supports Avalon Memory Mapped custom logic

- SGDMA Engine supports Avalon Streaming burst access devices

-

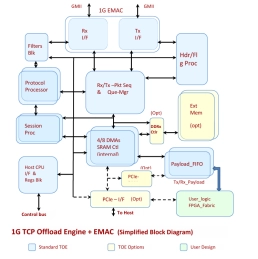

1G TCP Offload Engine TOE Very Low Latency (TOE)

- Ideal for high performance and mid performance specialized, differentiable ASICs or FPGAs for Network security or Network infrastructure applications

- Less than 4000 Xilinx slices, Altera ALMs or 150,000 ASIC gates + on-chip memory

- Fully integrated 100 M bit/1-G bit high performance EMAC.

- Scalable MAC Rx FIFOs and Tx FIFOs make it ideal for optimizing system performance.

-

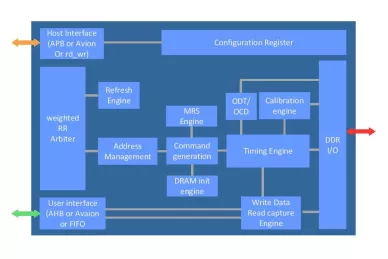

DDR-I/II/III CONTROLLER IP CORE

- Compliant with JEDEC Standard.

- Support up to 4 Gb and 8 banks of DDR2 devices.

- Application bus – FIFO, AHB, Avalon. Support multiple agents on application bus interface with built-in credit/aging based weighted round robin arbitration scheme.

- Programmable CAS latency and DRAM timing parameters.

-

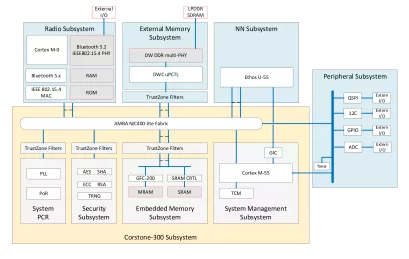

IP platform for intelligence gathering chips at the Edge

- High performance IoT solutions for AI at the Edge can now be created up to 30% faster

-

Display controller for dual-display

- Scan directions: 90/180/270° rotation, horizontal/vertical flip

- Multiple layers (alpha blend) with configurable mapping

-

2D Blit and Raster Graphics

- All buffer formats 100% compatible

- Flexible pixel formats (1/2/4/8/16/18/24/32 bpp; any bit width per channel)

- YUV support (packed, planar, 4:4:4, 4:2:2, 4:2:0, progressive, interlaced)

- Dynamic re-configuration of processing units

-

ISDB-T Demodulator

- Full 13-segment ISDB-T demodulator

- ARIB STD-B31 compliant supporting 1, 2 or 3-layers

- High-performance demodulation engine for demanding applications

- Sophisticated channel impairment correction

-

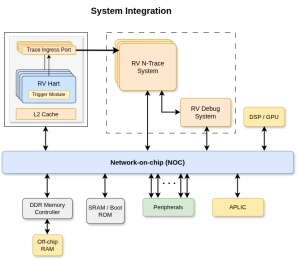

RISC-V Debug & Trace IP

- 10xEngineers Debug & N-Trace IP delivers a unified Debug + Trace solution that provides full-system visibility with low overhead and multi-hart awareness.

- Standards-compliant debug, real-time trace, and flexible triggering significantly reduce bring-up time and simplify system integration.

-

LPDDR5/4/4X PHY in Samsung (14nm) for Automotive

- Low latency, small area, low power

- Compatible with JEDEC standard LPDDR5 SDRAMs up to 6400 Mbps

- Compatible with JEDEC standard LPDDR4 and LPDDR4X SDRAMs up to 4267 Mbps

- DFI 5.0 compliant interface to the memory controller