Arasan IP

Filter

Compare

117

IP

from

2

vendors

(1

-

10)

-

-

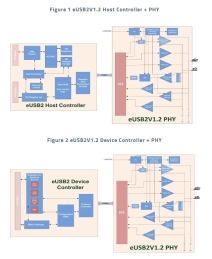

eUSB2V1.2 Controller + PHY IP

- eUSB2 can support USB high-speed, full-speed, and low-speed operation, as well as the USB 2.0 L1/L2 link power management requirements. In addition, eUSB2 requires no change to the existing USB 2.0 software programming model.

- eUSB2 also uses the same two data line configurations, eD+ and eD- as USB2 D+ and D-. Vbus and power delivery are not impacted by eUSB2.

-

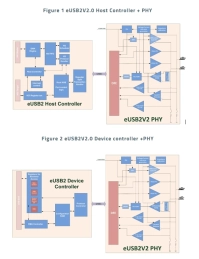

eUSB2V2.0 Controller + PHY IP

- While traditional eUSB2 meets basic connectivity needs at 480 Mbps, modern SoCs and peripherals demand significantly higher throughput.

- eUSB2-V2.0 bridges this gap by delivering up to 10× performance improvement, along with better power efficiency and EMI control — without changing the fundamental USB 2.0 software ecosystem.

-

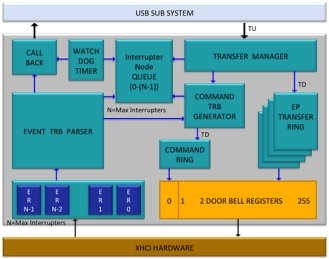

USB 3.0 xHCI Driver software

- Compliant with eXtensible Host Controller Interface for USB 3.0 version 0.9

- Portability in choice of OS, processors and hardware

- Easy-to-use interface for applications

- Fully documented generic device operation API

-

USB 3.0 Device Upgrade IP Core

- The USB 3.0 Device Upgrade provides a dedicated dual simplex, routable packet architecture for USB3.0 packet transfers, with a disable option for power savings.

- The USB 3.0 Upgrade IP supports all power management features as well as a dedicated link manager for each downstream port for increased efficiency.

-

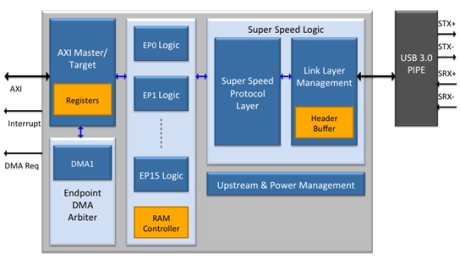

USB 3.0 Device

- USB 3.0 Compliance

- SuperSpeed: 5 Gbit/s

- Hish Speed: 480Mbit/s

- Full Speed: 12Mbit/s

- 8/16/32 bit USB 3.0 PIPE interface

-

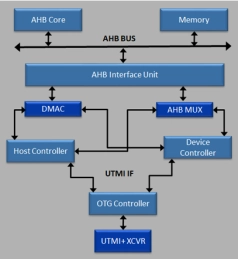

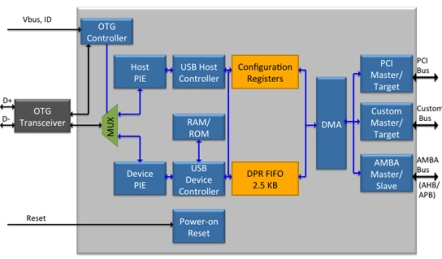

USB 2.0 OTG Dual Role Device (DRD) Controller

- Compliant with OTG Supplement Rev. 1.0a

- USB 2.0 Compliant

- Supports 480 Mbit/s (HS), 12 Mbit/s (FS), and 1.5 Mbit/s (LS)

- Supports Session Request Protocol (SRP) and Host Negotiation Protocol (HNP)

-

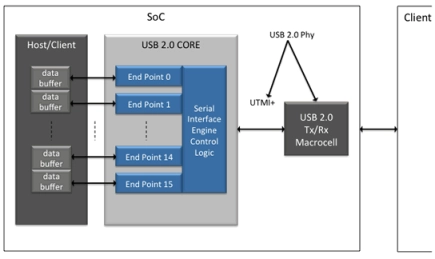

USB 2.0 PHY IP core

- Complies with USB specifications, rev. 2.0 and 1.1

- Complies with UTMI+ specification, level 3, rev. 1.0

- Supports 480Mb/s (HS), 12Mb/s (FS) and 1.5MB/s (LS) serial data transmission rates

- Supports 8-bit unidirectional Parallel Interface Engine (PIE) bus for HS, FS and LS modes, and Serial Interface Engine (SIE) for FS and LS modes

-

USB 2.0 OTG IP Core

- High speed support: 480 Mbit/s

- Full speed support: 12 Mbit/s

- USB 2.0 Compliant

- High/Full speed support using 8/16 bit UTMI/ULPI interface

-

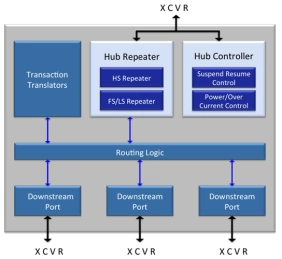

USB 2.0 Hub IP Core

- The USB 2.0 Hub IP core is a USB 2.0 specification compliant hub core that supports 480 Mbit/s in High Speed (HS) mode, 12 Mbit/s in Full Speed (FS) mode, and 1.5 Mbit/s in Low Speed (LS) mode.

- The USB 2.0 Hub IP core consists of the Hub Controller, Hub Repeater, Transaction Translators, Routing Logic, and Downstream Ports.