Achronix IP

Filter

Compare

4

IP

from

3

vendors

(1

-

4)

-

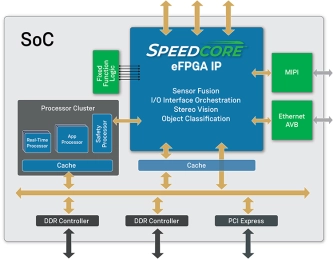

Embedded FPGA

- Speedcore embedded FPGA (eFPGA) IP has brought the performance and flexibility of programmable logic to ASICs and SoCs.

- Customers can integrate a Speedcore eFPGA IP into an ASIC or SoC for high-performance, compute-intensive and real-time processing applications such as artificial intelligence (AI), machine learning (ML), 5G wireless, networking, storage and automotive.

-

Chacha20-Poly1305 IP for FPGA and ASIC

- Available in 2 versions:

- Fast : High bandwith with low latency and high frequency

- Small : Higher latency but smaller footprint

- Full standard support : Zyxx ChaCha20-Poly1305 supports full specification of the ChaCha20-Poly1305 standard

-

Configurable Ascon IP for FPGA and ASIC

- Available in different configurations :

- ? Ascon-128 for authenticated encryption with 64 bits data blocks

- ? Ascon-128a for authenticated encryption with 128 bits data

- blocks

-

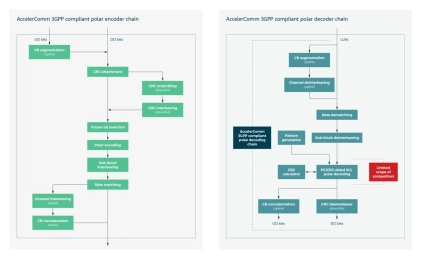

Polar Encoder / Decoder for 3GPP 5G NR

- The patented polar encoding and decoding IP for the 3GPP New Radio uplink and downlink includes the entire processing chain, to provide quick and easy integration and minimize the amount of extra work needed.

- The polar core uses PC- and CRC-aided SCL polar decoding techniques, in order to achieve compromise-free error correction performance.