AXI IP

Filter

Compare

1,531

IP

from

162

vendors

(1

-

10)

-

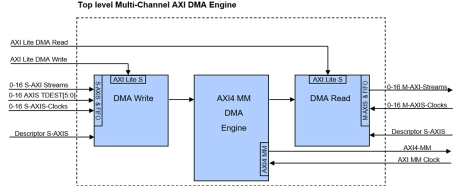

Multi-Channel AXI DMA Engine

- The Multi-Channel AXI DMA engine IP Core for AXI4 is a powerful programmable AXI Stream to AXI memory mapped bridge with sophisticated data addressing options.

- These features allow data accesses on a tile basis in order to address regions of interest (ROI) based applications like stereo cameras, 2D picture compression algorithms and others.

-

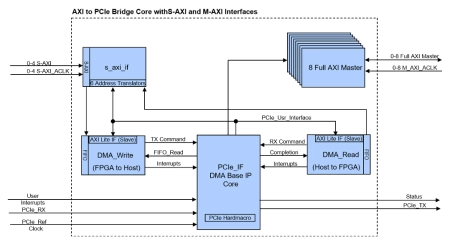

AXI Bridge for PCIe IP Core

- The AXI Bridge for PCIe IP core is the IP solution with a powerful mix of multiple industry standard memory mapped AXI Interfaces.

- The AXI Bridge IP core translates the AXI4 memory read or writes to PCI-Express Transaction Layer Packets and translates PCIe memory read and write requests to AXI4 transactions.

- All interfaces support fully parallel operation without any interferences. Interfaces that are not required can be turned off individually and do not occupy logic resources.

-

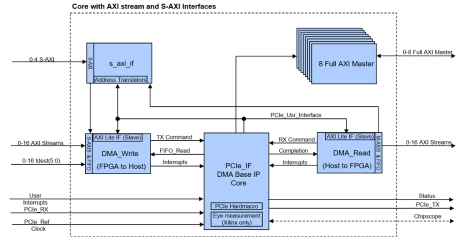

AXI Bridge with DMA for PCIe IP Core

- The AXI Bridge with DMA IP core is the ultimate PCIe DMA IP solution with a powerful mix of multiple industry standard AXI Interfaces.

- AXI Stream interfaces allow continuous data streaming from FPGA to Host or from Host to FPGA. S-AXI Memory mapped interfaces allow easy data access of remote memories in order to realize shared memory access or per to peer applications.

-

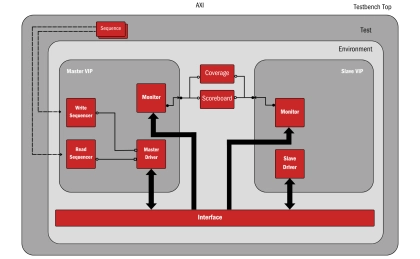

Siemens EDA* AXI Verification IP Suite

- The Siemens EDA AXI Verification IP Suite (Intel® FPGA Edition) provides bus functional models (BFMs) to simulate the behavior and to facilitate the verification of intellectual property (IP) that conforms to the Advanced Microcontroller Bus Architecture Advanced eXtensible Interface (AMBA* AXI) Protocol, with restrictions to simplify the application programming interface (API) for you.

-

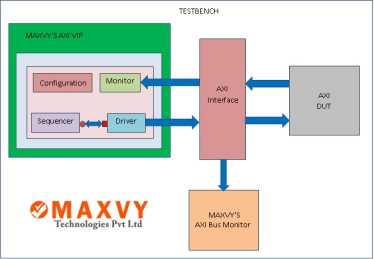

AXI Verification IP

- The AMBA-AXI VIP provides a complete solution for verification of AMBA-AXI protocol version 2.0

- The AXI verification IP is fully compatible with standard AXI 3 protocol

- This VIP is supported natively in System Verilog UVM

-

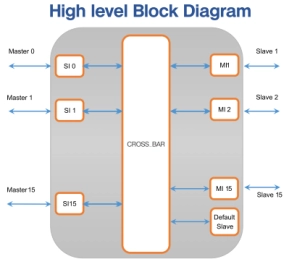

AXI Interconnect

- The AXI MATRIX-IP component is a multi-layer interconnect implementation of the AXI protocol, which is designed for high-performance, high-frequency system designs.

- AXI MATRIX-IP is highly configurable with the capacity to handle up to 16 Masters and Slaves. IP can be configured to support AXI3, AXI4-Lite or AXI4

-

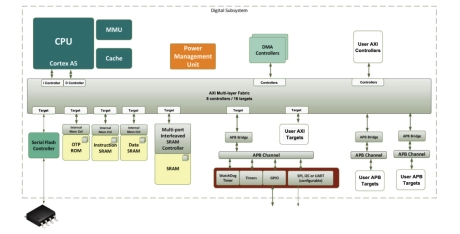

AXI Performance Subsystem - ARM Cortex A

- The AXI Performance Subsystem is an AMBA® AXI4 based system that is useful as the digital infrastructure for building SOCs needing high performance.

- This system contains an 8 Master component, 16 Slave component AXI4 multi-matrix for supporting multiple high speed user AXI Master components while providing high performance with Cortex-A5 class processors.

-

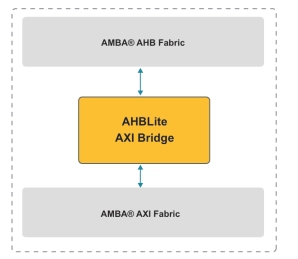

AHB Lite to AXI Bridge

- The AHB Lite to AXI Bridge translates an AHB Lite bus transaction (read or write) to an AXI bus transaction.

- It is expected that the AXI clock and the AHB clock are derived from the same clock source, and that the period of the AHB Lite clock is an integer multiple of the AXI clock in the range [1,16].

-

-

AMBA AXI - Validates AXI interface functionality, performance, and compliance

- The AMBA AXI Verification IP from XtremeSilica is a powerful tool designed to validate the functionality, performance, and protocol compliance of AXI interfaces in SoCs. It supports AXI3, AXI4, and AXI4-Lite protocols, ensuring efficient data transfers across systems.

- This versatile VIP is crucial in validating high-performance systems, enabling seamless communication between memory, processors, and peripherals. It is widely used in industries like AI, IoT, automotive, and high-speed computing for complex transaction scenarios