AMBA Multi-Channel DMA Controller IP

Filter

Compare

6

IP

from

3

vendors

(1

-

6)

-

SG DMA Controller, 1-16 DMA Channels, AXI4 / AXI3 Master Interfaces

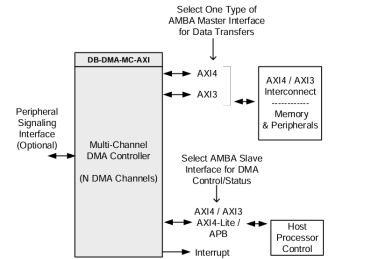

- The DB-DMAC-MC-AXI Verilog RTL IP Core is a Multi-Channel DMA Controller supporting 1 – 16 independent data transfers.

- The Direct Memory Access (DMA) Controller IP Core contains 1 - 16 DMA Controller Engines (i.e. DMA Channels), with user selectable AMBA AXI4 / AXI3 Master Read/Write interconnects.

- The DB-DMAC-MC-AXI excels at high data throughput on both small and large data sets. Standard IP releases of number of DMA Controller Engines are 1, 2, 4, 8, 16.

-

SG DMA Controller, 1-16 DMA Channels, AHB5 Master Interface

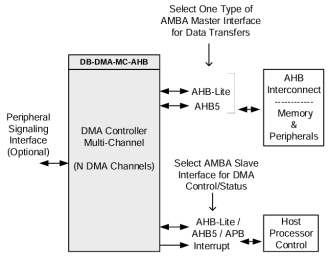

- The DB-DMAC-MC-AHB5 & DB-DMAC-MC-AHB-Lite Verilog RTL IP Core is a Multi-Channel DMA Controller supporting 1 – 16 independent data transfers.

- The Direct Memory Access (DMA) Controller IP Core contains 1 - 16 DMA Controller Engines (i.e. DMA Channels), with a unified AHB Master Read/Write interconnects.

- The DB-DMAC-MC-AHB excels at high data throughput on both small and large data sets. Standard IP releases of number of DMA Controller Engines are 1, 2, 4, 8, and 16.

-

PCIe DMA Controller (Low Latency)

- Implements standard Transaction layer functions e.g. TLP generation/reception, TLP completion handling and interrupt generation

- Implements 32-bit, 64-bit, 128-bit and 256-bit User application. (Width selection is based on PCIe endpoint interface width)

- PCIe Gen1, Gen2 and Gen3 support.

- Up to 8 independent DMA channels with each channel capable of operating in Block-DMA or Scatter-Gather DMA modes

-

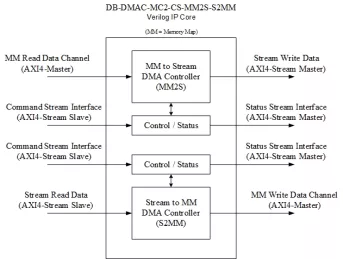

AXI4-Stream to/from AXI Memory Map – 2 DMA Channels - Control by SGL Commands Streams

- The DB-DMAC-MC2-CS-MM2S-S2MM Verilog RTL IP Core is a Multi-Channel Scatter-Gather DMA Controller that transfers data between AXI4 Memory Map and AXI4-Stream Interfaces.

- Descriptor Control is managed by Commands that stream in via dedicated Command, AXI4-Stream Interface, with resulting output Status on Status Stream, AXI4-Stream Interfaces.

-

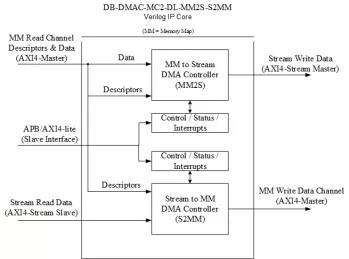

AXI4-Stream to/from AXI Memory Map – 2 DMA Channels - Control by SGL Descriptors

- The DB-DMAC-MC2-DL-MM2S-S2MM Verilog RTL IP Core is a Multi-Channel Scatter-Gather DMA Controller that transfers data between AXI4 Memory Map and AXI4-Stream Interfaces.

- Control is managed by Descriptors initialized by the Control/Status Register Interface, with the Descriptors read in from memory via the AXI4 MM Read Channel and processed with the DMA data transfer information.

-

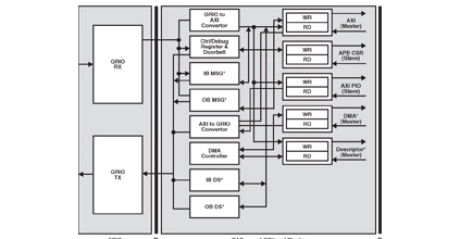

RapidIO to AXI Bridge (RAB)

- The RapidlO-AXI Bridge (RIO-AXI Bridge) is a highly flexible and configurable IP used along with the native RapidlO Controller (GRIO) to provide RapidlO interface on one side and AXI interface on the system side.

- The Bridge has been architectured to interface with a RapidlO controller used as a Host or device.

- The RIO-AXI BRIDGE uses high speed multi-channel DMA Messaging and data streaming controllers to match the bandwidth requirements of the RIO solution.