40G TCP Endpoint IP

Filter

Compare

6

IP

from

4

vendors

(1

-

6)

-

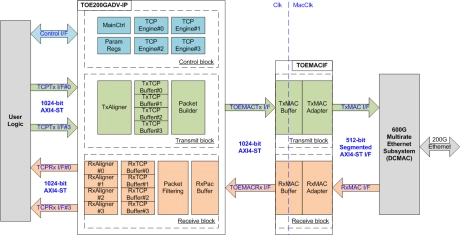

200G / 100G / 40G / 25G / 10G / 1G TCP Offloading Engine

- The TCP Offloading Engine IP core (TOE200G/100G/40G/25G/10G/1G-IP) is the epochal solution implemented without CPU.

- Generally, TCP processing is so complicated that expensive high-end CPU is required.

- TOE-IP core series built by pure hardwired logic can take place of such extra CPU for TCP protocol management.

-

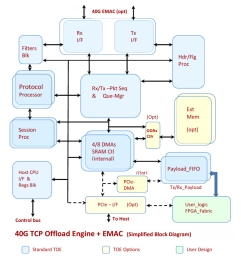

100G bps Full TCP & UDP Offload Engine

- Increase your TCP and UDP Network actual performance by up to 600%

- Built around Proven and Mature TCP and UDP technology since 2009.

- 40G: In production. Performed Live demo of 40G at Super Computing 2015

- Qualified on Altera/Intel and Xilinx. FPGA Subsystems Solutions available now

- First company to implement and deliver Full TCP Stack in High performance FPGA in 2009.

-

40G-1K Sess. TCP + UDP Offload Engine

- Highly customizable hardware IP block. Easily portable to ASIC flow, Xilinx/Altera FPGAs or Structured/ASIC flow.

- Eighth Generation TOE and System Solutions provide ‘Ultra-Low Latency’ and Ultra-High Performance with highest TCP bandwidth in Full Duplex. Network Tested and mature TCP protocol offload implementation

- All stages of Full TCP stack implemented in High performance hardware

-

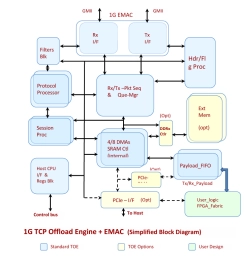

1G TCP Offload Engine TOE +PCIe Very Low Latency (TOE+PCIe)

- INT 1012 is the only SOC that integrates 1G TOE + 1 GEMAC + PCIe/DMA + Host interfaces in the smallest logic footprint.

- It is highly flexible that is customizable for layer-3, layer 4-7 network infrastructure and network security systems applications.

-

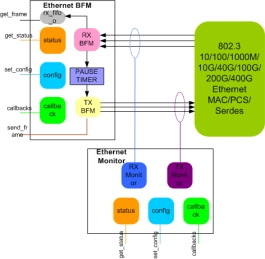

Ethernet - up to 800G Verification IP

- Supports 2.5G and 5G Speeds as per 802.3cb

- 2.5GBASE-KX

- 5GBASE-KR

- 2.5GBASE-T

-

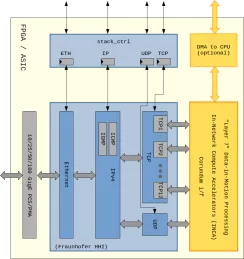

TCP/UDP/IP Network Protocol Accelerator Platform

- Highly modular TCP/UDP/IP stack implementation in synthesizable HDL

- Full line rate of 70 Gbps or more in FPGA, 100 Gbps or more in ASIC

- 128-bit wide bi-directional data paths with streaming interfaces

- Multiple, parallel TCP engines for scalable processing